HIGH-RESOLUTION REFLECTIVE ABSOLUTE ENCODER

#### Rev F1, Page 1/85

#### FEATURES

- Reflective, compact, high-resolution, absolute encoder iCs

- ♦ Series of 3 basic encoder iCs for matched code discs (∅ 9 mm, 26 mm) and linear scales (max. 6.71 m)

- ♦ Unique *FlexCode*<sup>®</sup> circuitry for arbitrary code disc diameters

- Monolithic HD Phased Array with excellent signal matching

- EncoderBlue<sup>®</sup>: System-on-chip design with embedded blue LED for excellent signal quality

- LED power control

- ♦ Absolute singleturn resolution of 22 bit (Ø 26 mm) with on-chip interpolation

- Automatic adjustment features on command

- Calibration and configuration storage via external I2C EEPROM

- Digital BiSS, SSI, and SPI interfaces with CMOS I/O

- Operational and temperature monitoring with alarm messaging

- ♦ Operation at 4.5 V to 5.5 V within -40 °C to 125 °C

- ♦ 2.5 V, 3.3 V, and 5.0 V compatible I/O ports

- ♦ Unique *FlexCount*<sup>®</sup> interpolation for arbitrary ABZ resolution

- UVW commutation signals for motors with 1 to 32 pole pairs

- Configurable analog outputs

- Absolute Data Interface (ADI) to multiturn sensors

- Wide assembly tolerances ensure easy installation

#### APPLICATIONS

- Low-height, absolute optical position encoders

- Factory automation and robotics

- Servo motors

- Linear actuators

#### PACKAGES

optoQFN32-5x5 5 mm x 5 mm x 0.9 mm RoHS compliant

#### Rev F1, Page 2/85

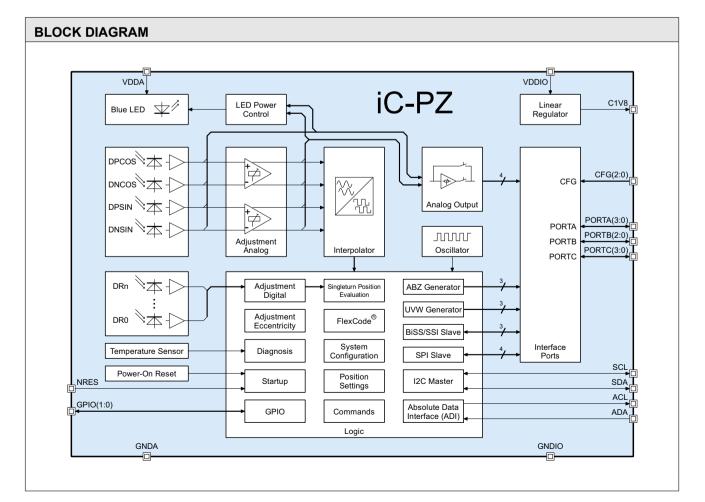

#### DESCRIPTION

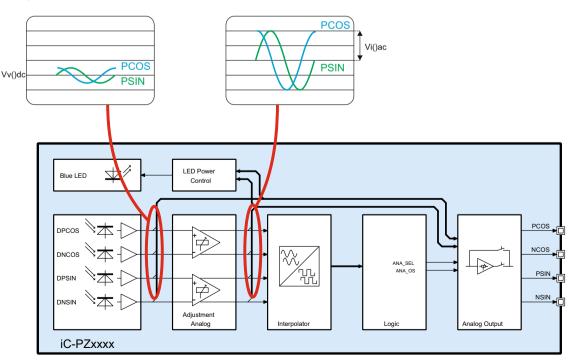

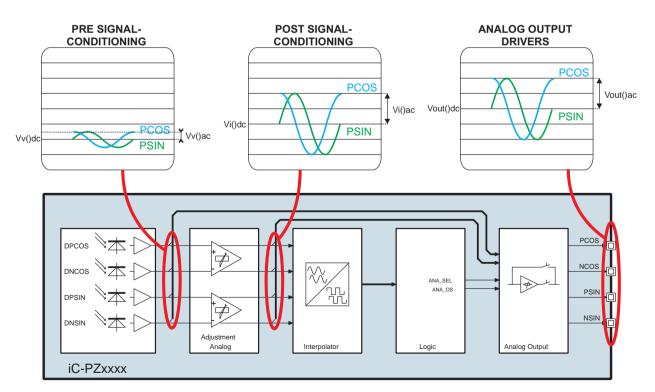

The iC-PZ Series represents advanced optical-reflective absolute encoder iCs featuring integrated photosensors. Utilizing an *HD Phased Array* and an *Embedded Blue LED Chip*, an outstanding signal fidelity is obtained at relaxed alignment tolerances.

Typical applications are high-resolution rotary and linear position encoders.

Blue-enhanced photosensors are adapted to the short wavelength of the embedded blue LED, improving the signal contrast for an outstanding jitter performance. The optical crosstalk is minimized due to the unique assembly technology of the emitter and sensor.

The internally powered blue LED ensures constant illumination without any external wiring. A sine square or sum control mode is selectable for LED power control.

Automatic adjustment features provide fast and reliable signal calibration on command.

Unique features like FlexCount<sup>®</sup> and FlexCode<sup>®</sup> guarantee highest flexibility regarding encoder resolution and diameter.

The configuration and calibration data is stored in an external I2C EEPROM. Additional user data can be stored and accessed via iC-PZ.

The analog circuitry and the integrated blue LED are operated at 5 V  $\pm$  10 %. For the digital supply includ-

ing the I/O ports, a voltage range of 2.25 V to 5.5 V is possible. Both supply inputs can be shorted and operated at 5 V.

BiSS, SSI, and SPI are supported as digital interfaces to ensure easy system-integration.

General notice on materials under excessive conditions

Epoxy resins (such as solder resists, IC package and injection molding materials, as well as adhesives) may show discoloration, yellowing, and surface changes in general when exposed long-term to high temperatures, humidity, irradiation, or due to thermal treatments for soldering and other manufacturing processes.

Equally, standard molding materials used for IC packages can show visible changes induced by irradiation, among others when exposed to light of shorter wavelengths, blue light for instance. Such surface effects caused by visible or IR LED light are rated to be of cosmetic nature, without influence to the chip's function, its specifications and reliability.

Note that any other material used in the system (e.g. varnish, glue, code disc) should also be verified for irradiation effects.

General notice on application-specific programming

Parameters defined in the datasheet represent supplier's attentive tests and validations, but - by principle - do not imply any warranty or guarantee as to their accuracy, completeness or correctness under all application conditions. In particular, setup conditions, register settings and power-up have to be thoroughly validated by the user within his specific application environment and requirements (system responsibility).

The chip's performance in application is impacted by system conditions like the quality of the optical target, the illumination, temperature and mechanical stress, sensor alignment and initial calibration.

HIGH-RESOLUTION REFLECTIVE ABSOLUTE ENCODER

Rev F1, Page 3/85

### CONTENTS

| PACKAGING INFORMATION<br>SENSOR LAYOUT                             | <b>5</b><br>5  |

|--------------------------------------------------------------------|----------------|

| PIN CONFIGURATION                                                  |                |

| oQFN32-5x5 (5 mm x 5 mm)                                           | 6<br>7         |

| ABSOLUTE MAXIMUM RATINGS                                           | 8              |

| THERMAL DATA                                                       | 8              |

| ELECTRICAL CHARACTERISTICS<br>ELECTRICAL CHARACTERISTICS: Diagrams | <b>9</b><br>12 |

| OPERATING REQUIREMENTS                                             | 13             |

| Supply Voltages                                                    | 13             |

| BiSS Slave                                                         | 14<br>15       |

| SPI Slave                                                          | 15             |

| Absolute Data Interface (ADI)                                      | 17             |

| SIGNAL DEFINITIONS                                                 | 18             |

| LINEAR REGULATOR                                                   | 19             |

| EEPROM SELECTION                                                   | 19             |

| POWER-ON RESET                                                     | 19             |

| STARTUP                                                            | 19             |

| INTERFACE PORTS                                                    | 20             |

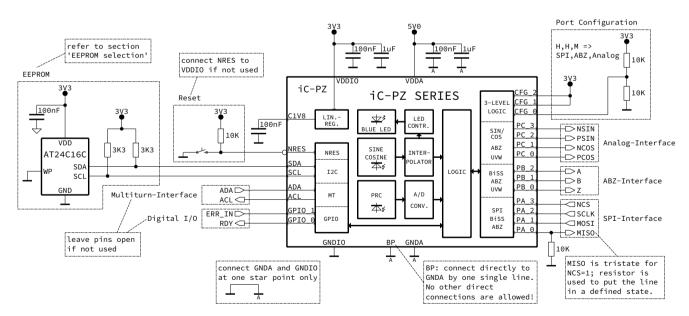

| CIRCUIT DESIGN PROPOSALS                                           | 21             |

| MEMORY ORGANIZATION                                                | 22             |

| EEPROM Access                                                      | 22             |

| Bank Selection                                                     |                |

| Register Protection Level (RPL)                                    | 22             |

| REGISTER MAP                                                       | 23             |

| INTERFACE PORTS CONFIGURATION                                      | 29             |

| Slew Rate I/O-Pads                                                 | 29             |

| Port Disabling                                                     |                |

|                                                                    | 29             |

| LED POWER CONTROL                                                  | 30             |

| INTERPOLATOR                                                       | 31             |

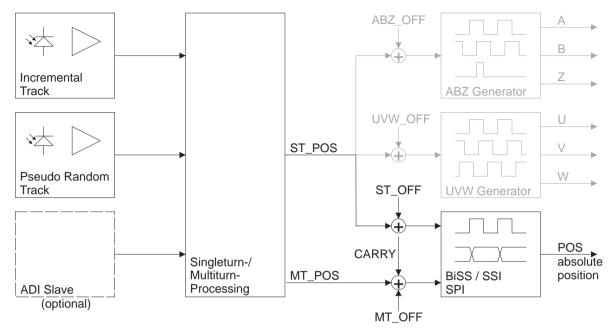

| SINGLETURN POSITION EVALUATION                                                                                                                                                                                                                                                                                                                                                  | 31                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

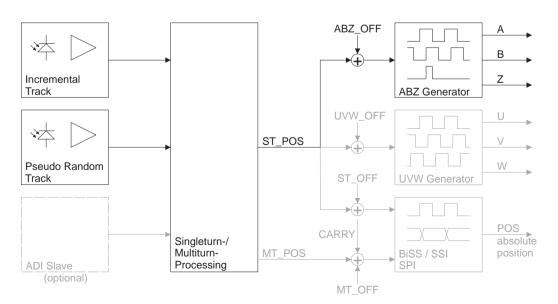

| Signal Routing                                                                                                                                                                                                                                                                                                                                                                  | <b>32</b><br>32<br>32                                     |

|                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |

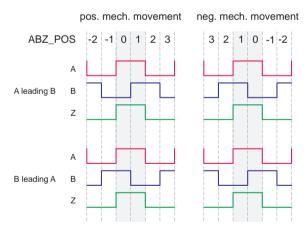

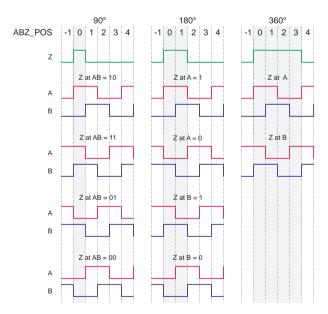

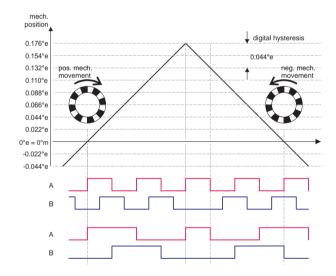

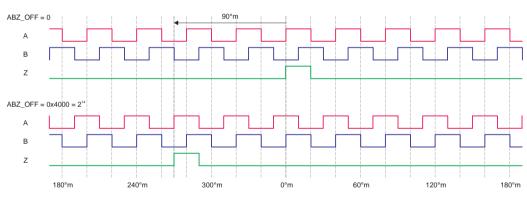

| AB PeriodsAB DirectionZ GatingZ PolarityHysteresisMinimum Transition DistanceABZ OffsetABZ Preset                                                                                                                                                                                                                                                                               | <b>33</b><br>33<br>34<br>34<br>34<br>35<br>36<br>36<br>36 |

|                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |

| Pole Pairs, Direction and Polarity                                                                                                                                                                                                                                                                                                                                              | <b>38</b><br>39<br>39<br>40                               |

| POSITION SETTINGS                                                                                                                                                                                                                                                                                                                                                               | 41                                                        |

| Position Offset                                                                                                                                                                                                                                                                                                                                                                 | 41<br>41<br>41                                            |

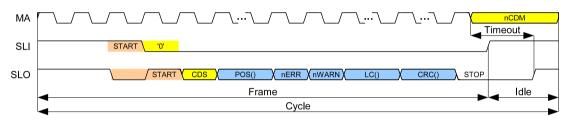

| BISS SLAVE                                                                                                                                                                                                                                                                                                                                                                      | 43                                                        |

| Single Cycle Data       Sign-of-Life Counter         Cyclic Redundancy Check       Sign-of-Life Counter         Fixed & Adaptive Timeout       Sign-of-Life Counter                                                                                                                                                                                                             | 43<br>44<br>44<br>44                                      |

| SSI SLAVE                                                                                                                                                                                                                                                                                                                                                                       | 46                                                        |

| Read Registers       Write Registers         Write Registers       Read Position         Read Position       Read Position         Write Command       Read Position         Read Diagnosis       Read Position         Request Data From I2C Slave       Read Position         Transmit Data To I2C Slave       Read Position         Get Transaction Info       Read Position | <b>48</b><br>48<br>49<br>50<br>51<br>51<br>51             |

| 0                                                                                                                                                                                                                                                                                                                                                                               | 52<br>52                                                  |

HIGH-RESOLUTION REFLECTIVE ABSOLUTE ENCODER

Rev F1, Page 4/85

| COMMANDS                                                                                                                                                                                                             | 53                                            | FLEXCODE®                                                                                                                                | 69                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

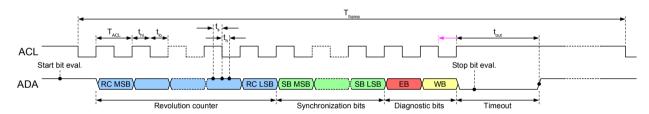

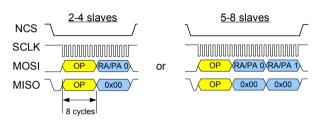

| ABSOLUTE DATA INTERFACE (ADI)         Interface Enable         Single- and Multi-Slave Operation         Synchronization         Error and Warning Bits         Interface Settings         Startup         Diagnosis | <b>55</b><br>55<br>56<br>56<br>57<br>58<br>58 | ADJUSTMENT ANALOG         Offset                                                                                                         | <b>70</b><br>71<br>72<br>73<br>74<br>74 |

| I2C MASTER         Communication with 8-bit devices         Communication with 16-bit devices         GPIO         GPIO as Input                                                                                     | 60<br>60<br>60<br>62<br>62                    | ADJUSTMENT DIGITAL         Adjustment Digital, Static         Adjustment Digital, Dynamic         Adjustment Digital, Applied Correction | <b>75</b><br>75<br>76<br>76             |

| GPIO as Output                                                                                                                                                                                                       | 62                                            | ADJUSTMENT ECCENTRICITY                                                                                                                  | 77                                      |

| TEMPERATURE SENSOR                                                                                                                                                                                                   | 63                                            | SAFETY ADVICE                                                                                                                            | 78                                      |

| DIAGNOSIS<br>Errors & Warnings                                                                                                                                                                                       | <b>64</b><br>66<br>66                         | HANDLING ADVICE                                                                                                                          | 78<br>79                                |

| SYSTEM CONFIGURATION<br>Revision & Identification                                                                                                                                                                    | <b>67</b><br>67<br>67                         | DESIGN REVIEW: Notes On Chip Functions                                                                                                   | 80                                      |

| BiSS Profile & Identifier                                                                                                                                                                                            | 68                                            | REVISION HISTORY                                                                                                                         | 81                                      |

HIGH-RESOLUTION REFLECTIVE ABSOLUTE ENCODER

Rev F1, Page 5/85

#### PACKAGING INFORMATION

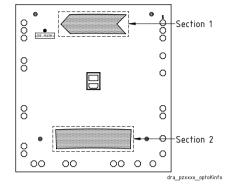

#### SENSOR LAYOUT

| AOI CRITERIA<br><die mark=""> <section> <area class=""/><sup>1</sup><br/>iC PZyyyy 1 A16</section></die> |                     |                    |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------|--------------------|--|--|

| <die mark=""></die>                                                                                      | <section></section> | <area class=""/> 1 |  |  |

| iC-PZxxxx                                                                                                | 1                   | A16                |  |  |

|                                                                                                          | 2                   | A25                |  |  |

<sup>1</sup> Inspection class for the optical inspection of detector areas. Refer to Optical Selection Criteria for further description.

#### Rev F1, Page 6/85

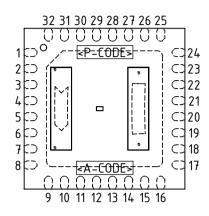

#### **PIN CONFIGURATION** oQFN32-5x5 (5 mm x 5 mm)

#### **PIN FUNCTIONS**

| No.                              | Name                                                                    | Function                                                                                                                                                                                                                                |

|----------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |                                                                         | Port Configuration Input<br>Interface Port A                                                                                                                                                                                            |

| 10<br>11<br>12<br>13<br>14<br>15 | PORTA(1)<br>PORTA(0)<br>C1V8<br>GNDIO <sup>3</sup><br>VDDIO<br>PORTB(2) | Interface Port A<br>Interface Port A<br>Interface Port A<br>Core Voltage Buffer Capacitance<br>(see Elec. Char. R01)<br>Digital I/O Ground<br>+2.25 V+5.5 V Digital I/O<br>Supply Voltage Input<br>Interface Port B<br>Interface Port B |

| 18<br>19<br>20<br>21<br>22<br>23 | ACL<br>ADA<br>GPIO(1)<br>GPIO(0)<br>NRES<br>PORTC(3)                    | Interface Port B<br>Absolute Data Interface, clock line<br>Absolute Data Interface, data line<br>General Purpose I/O<br>General Purpose I/O<br>Reset Input<br>Interface Port C<br>Interface Port C                                      |

| 26<br>27<br>28<br>29<br>30<br>31 |                                                                         | Interface Port C<br>Interface Port C<br>I2C Master, clock line<br>I2C Master, data line<br>Analog Ground<br>+4.5 V+5.5 V Analog<br>Supply Voltage Input<br>Port Configuration Input<br>Port Configuration Input                         |

|                                  | n.c. <sup>1</sup>                                                       | Port Configuration input                                                                                                                                                                                                                |

|                                  | BP <sup>2</sup>                                                         | Backside Pad / Exposed Pad                                                                                                                                                                                                              |

IC top marking: <P-CODE> = product code, <A-CODE> = assembly code (subject to changes);

- <sup>1</sup> Pin numbers marked with n.c. are not connected.

<sup>2</sup> The backside pad has to be connected by a single link to GNDA. A current flow across the pad is not permissible.

- <sup>3</sup> GNDA and GNDIO must be at the same potential but should be connected with separate lines from a star point on the PCB.

HIGH-RESOLUTION REFLECTIVE ABSOLUTE ENCODER

Rev F1, Page 7/85

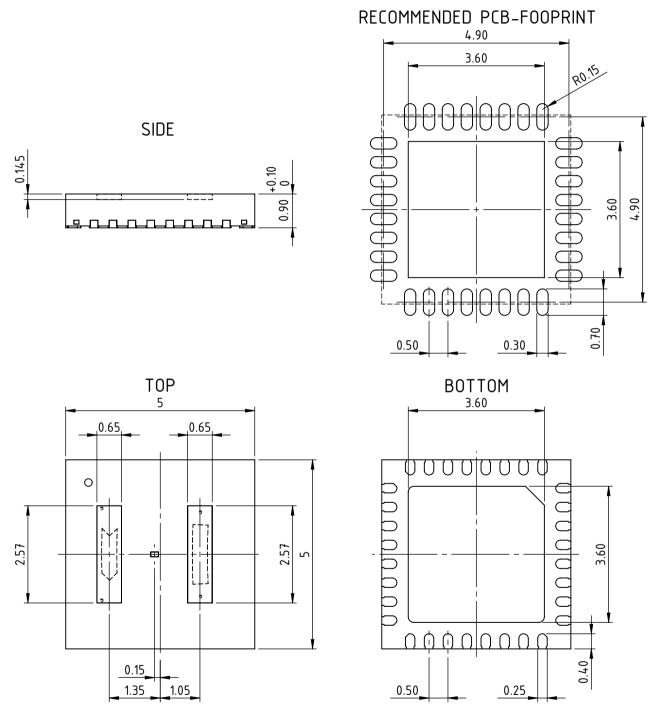

#### PACKAGE DIMENSIONS

All dimensions given in mm. General Tolerances of form and position according to JEDEC MO-220. Positional tolerance of sensor pattern:  $\pm 70\mu$ m /  $\pm 1^{\circ}$  (with respect to center of backside pad). Maximum molding excess  $\pm 20\mu$ m /  $-75\mu$ m versus surface of glass. Small pits in the mold surface, which may occasionally appear due to the manufacturing process, are cosmetic in nature and do not affect reliability.  $\frac{dra_ogfn32-5x5-4_pzxxxx\_0_pack\_1, 10:1}{dra_ogfn32-5x5-4_pzxxxx\_0_pack\_1, 10:1}$

Rev F1, Page 8/85

#### **ABSOLUTE MAXIMUM RATINGS**

Beyond these values damage may occur; device operation is not guaranteed.

| Item | Symbol   | Parameter                       | Conditions                                                    | 1    |                | Unit |

|------|----------|---------------------------------|---------------------------------------------------------------|------|----------------|------|

| No.  |          |                                 |                                                               | Min. | Max.           |      |

| G001 | VDDA     | Voltage at VDDA                 | Referenced to GNDA                                            | -0.3 | 6              | V    |

| G002 | I(VDDA)  | Current in VDDA                 |                                                               | -20  | 100            | mA   |

| G003 | VDDIO    | Voltage at VDDIO                | Referenced to GNDA                                            | -0.3 | 6              | V    |

| G004 | I(VDDIO) | Current in VDDIO                |                                                               | -20  | 100            | mA   |

| G005 | GNDIO    | Voltage at GNDIO                | Referenced to GNDA<br>Supply voltage at VDDA or VDDIO applied | -0.3 | 0.3            | V    |

| G006 | V(C1V8)  | Voltage at C1V8                 | Referenced to GNDIO                                           | -0.3 | 2.0            | V    |

| G007 | I(C1V8)  | Current in C1V8                 |                                                               | -20  | 20             | mA   |

| G008 | V(PORTC) | Voltage at PORTC(3:0)           | Referenced to GNDA                                            | -0.3 | VDDA +<br>0.3  | V    |

| G009 | I(PORTC) | Current in PORTC(3:0)           |                                                               | -20  | 20             | mA   |

| G010 | V()      | Pin Voltage, all remaining pins | Referenced to GNDA                                            | -0.3 | VDDIO +<br>0.3 | V    |

| G011 | l()      | Pin Current, all remaining pins |                                                               | -20  | 20             | mA   |

| G012 | Vd()     | ESD Susceptibility              | HBM, 100 pF discharged through $1.5  k\Omega$                 |      | 2              | kV   |

| G013 | Tj       | Junction Temperature            |                                                               | -40  | 140            | °C   |

<sup>1</sup> JEDEC document JEP 155: 500V HBM allows safe manufacturing with a standard ESD control process

#### THERMAL DATA

| ltem | Symbol | Parameter                                | Conditions                                                                                                        |      |      |      | Unit |

|------|--------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| No.  |        |                                          |                                                                                                                   | Min. | Тур. | Max. |      |

| T01  | Та     | Operating Ambient Temperature Range      |                                                                                                                   | -40  |      | 125  | °C   |

| T02  | Ts     | Permissible Storage Temperature<br>Range |                                                                                                                   | -40  |      | 125  | °C   |

| T03  | Tpk    | Soldering Peak Temperature               | tpk < 20 s, convection reflow                                                                                     |      |      | 245  | °C   |

|      |        |                                          | MSL 3 (max. floor life 168 h at 30 °C and 60 %<br>RH); Refer to Handling and Soldering<br>Conditions for details. |      |      |      |      |

| T04  | Rthja  | Thermal Resistance Chip to Ambient       | Package mounted on PCB according to<br>JEDEC standard                                                             |      | 50   |      | K/W  |

All currents flowing into the device pins are positive; all currents flowing out of the device pins are negative.

Rev F1, Page 9/85

#### **ELECTRICAL CHARACTERISTICS**

| ltem<br>No. | Symbol          | Parameter                                                                                        | Conditions                                                                                                                                                                                                                                                                                                                                                                       | Min.               | Тур.                | Max. | Unit                                   |

|-------------|-----------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|------|----------------------------------------|

| Gene        | ral             | 1                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                  |                    |                     | I    | 11                                     |

| 001         | VDDA            | Analog Supply Voltage                                                                            | referenced to GNDA                                                                                                                                                                                                                                                                                                                                                               | 4.5                | 5.0                 | 5.5  | V                                      |

| 002         | I(VDDA)         | Analog Supply Current                                                                            | no external load, LED off<br>refer to Table 145 for details<br>without analog output buffer<br>with analog output buffer                                                                                                                                                                                                                                                         |                    | 18.4<br>22.2        |      | mA<br>mA                               |

| 003         | VDDIO           | I/O Supply Voltage                                                                               | referenced to GNDIO                                                                                                                                                                                                                                                                                                                                                              | 2.25               |                     | VDDA | V                                      |

| 004         | I(VDDIO)        | I/O Supply Current                                                                               | ports configured to BiSS/ABZ/Analog, default<br>register values, 600 RPM (iC-PZ2656)<br>VDDIO = 5.5 V, no external load, NRES = low<br>VDDIO = 2.25 V, no external load, NRES = high<br>VDDIO = 5.5 V, no external load, NRES = high                                                                                                                                             |                    | 3.8<br>14.5<br>15.0 |      | mA<br>mA<br>mA                         |

| 005         | SR(VDDIO)       | Slewrate of VDDIO                                                                                | in range 1.0 VVDDIOon                                                                                                                                                                                                                                                                                                                                                            | 25                 |                     |      | V/s                                    |

| 006         | V(C1V8)         | Digital Core Voltage                                                                             | generated internally                                                                                                                                                                                                                                                                                                                                                             | 1.62               | 1.8                 | 1.98 | V                                      |

| 007         | $\alpha$ ()e,mx | Maximum Permissible<br>Acceleration                                                              | $\begin{array}{l} \alpha()e = \frac{d_{\omega}}{dt} \mbox{ for sine/cosine} \\ \mbox{for linear systems: } a()mx = \frac{\alpha()e,mx}{2\pi} \cdot r_{nat} \\ \mbox{with } r_{nat} \mbox{ native resolution, i.e. line distance of} \\ \mbox{the incremental track on the scale} \\ \mbox{PZ01L: } r_{nat} = 204.8 \ \mu m \rightarrow a()mx = 6500 \ \frac{m}{s^2} \end{array}$ |                    |                     | 200  | 10 <sup>6</sup><br>rade/s <sup>2</sup> |

| Digita      | I I/O Pads      | 1                                                                                                | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                            |                    |                     |      |                                        |

| 201         | V()             | Pin-Open Voltage CFG(2:0)                                                                        |                                                                                                                                                                                                                                                                                                                                                                                  | 40                 | 50                  | 60   | %VDDIO                                 |

| 202         | Vt()hi          | Threshold high CFG(2:0)                                                                          |                                                                                                                                                                                                                                                                                                                                                                                  |                    |                     | 90   | %VDDIO                                 |

| 203         | Vt()med         | Threshold medium CFG(2:0)                                                                        |                                                                                                                                                                                                                                                                                                                                                                                  | 40                 |                     | 60   | %VDDIO                                 |

| 204         | Vt()lo          | Threshold low CFG(2:0)                                                                           |                                                                                                                                                                                                                                                                                                                                                                                  | 10                 |                     |      | %VDDIO                                 |

| 205         | Vt()hys         | Threshold Hysteresis<br>medium/high or low/medium<br>CFG(2:0)                                    |                                                                                                                                                                                                                                                                                                                                                                                  |                    | 10                  |      | %VDDIO                                 |

| 211         | Rpu()           | Pull-Up Resistor CFG(2:0)                                                                        | V(CFG) = 0 V                                                                                                                                                                                                                                                                                                                                                                     | 130                | 200                 | 280  | kΩ                                     |

| 212         | Rpd()           | Pull-Down Resistor CFG(2:0)                                                                      | V(CFG) = VDDIO                                                                                                                                                                                                                                                                                                                                                                   | 130                | 200                 | 280  | kΩ                                     |

| 213         | Vt()hi          | Threshold high NRES, GPIO(1:0),<br>SCL, SDA, ADA, PORTA(3:0),<br>PORTB(2:0), PORTC(3:0)          | pins of PORTA/B/C only if configured as inputs                                                                                                                                                                                                                                                                                                                                   |                    |                     | 70   | %VDDIO                                 |

| 215         | Vt()lo          | Threshold low NRES, GPIO(1:0),<br>SCL, SDA, ADA, PORTA(3:0),<br>PORTB(2:0), PORTC(3:0)           | pins of PORTA/B/C only if configured as inputs                                                                                                                                                                                                                                                                                                                                   | 30                 |                     |      | %VDDIO                                 |

| 217         | Vt()hys         | Threshold Hysteresis NRES,<br>GPIO(1:0), SCL, SDA, ADA,<br>PORTA(3:0), PORTB(2:0),<br>PORTC(3:0) | pins of PORTA/B/C only if configured as inputs                                                                                                                                                                                                                                                                                                                                   |                    | 15                  |      | %VDDIO                                 |

| 219         | lpu()           | Pull-Up Current NRES,<br>GPIO(1:0), ADA, PORTA(3:0),<br>PORTB(2:0), PORTC(3:0)                   | V() = GNDIO<br>pins of PORTA/B/C only if configured as inputs<br>pin GPIO(0) only for GPIO0_CFG = 00/01<br>pin GPIO(1) only for GPIO1_CFG = 00/01 and<br>IC not in reset                                                                                                                                                                                                         | -50                |                     | -8   | uA                                     |

| 220         | lpd()           | Pull-Down Current GPIO(1:0)                                                                      | V() = VDDIO<br>pin GPIO(0) only for GPIO0_CFG = 10<br>pin GPIO(1) only for GPIO1_CFG = 10 or IC in<br>reset                                                                                                                                                                                                                                                                      | 8                  |                     | 50   | uA                                     |

| 222         | lsc()hi         | Short-Circuit Current high<br>GPIO(1:0), ACL, PORTA(3:0),<br>PORTB(2:0), PORTC(3:0)              | V() = GNDIO, pins of PORTA/B/C only if configured as outputs<br>VDDIO = $2.5 V \pm 10 \%$<br>VDDIO = $3.3 V \pm 10 \%$<br>VDDIO = $5 V \pm 10 \%$                                                                                                                                                                                                                                | -55<br>-75<br>-120 | <br> <br> <br>      |      | mA<br>mA<br>mA                         |

Rev F1, Page 10/85

### ELECTRICAL CHARACTERISTICS

| ltem              | Symbol         | Parameter                                                                        | Conditions                                                                                                                                                                                                                                                                                             |          |                      |                        | Unit                 |

|-------------------|----------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------|------------------------|----------------------|

| <b>10.</b><br>224 | lsc()lo        | Short-Circuit Current lo<br>GPIO(1:0), SCL, SDA, ACL,                            | V() = VDDIO, pins of PORTA/B/C only if config-<br>ured as outputs                                                                                                                                                                                                                                      | Min.     | Тур.                 | Max.                   |                      |

|                   |                | PORTA(3:0), PORTB(2:0),<br>PORTC(3:0)                                            | $\begin{array}{l} \text{VDDIO} = 2.5  \text{V} \pm 10  \% \\ \text{VDDIO} = 3.3  \text{V} \pm 10  \% \\ \text{VDDIO} = 5  \text{V} \pm 10  \% \end{array}$                                                                                                                                             |          |                      | 55<br>75<br>120        | mA<br>mA<br>mA       |

| 226               | Vs()hi         | Saturation Voltage high<br>GPIO(1:0), ACL, PORTA(3:0),<br>PORTB(2:0), PORTC(3:0) | Vs()hi = VDDIO - V()<br>I() = -4 mA                                                                                                                                                                                                                                                                    |          |                      | 0.4                    | V                    |

| 227               | Vs()lo         | Saturation Voltage low GPIO(1:0),<br>ACL, PORTA(3:0), PORTB(2:0),<br>PORTC(3:0)  | I() = 4 mA                                                                                                                                                                                                                                                                                             |          |                      | 0.4                    | V                    |

| 228               | ls()lo         | Saturation Current low SCL, SDA                                                  | V() = 400 mV<br>V() = 600 mV                                                                                                                                                                                                                                                                           | 3<br>6   |                      |                        | mA<br>mA             |

| 229               | tr()           | Rise Time GPIO(1:0), ACL,<br>PORTA(3:0), PORTB(2:0),<br>PORTC(3:0)               | CL = 20 pF, rise 3070 % VDDIO<br>PADx_CFG = 00 and GPIO(1:0)<br>PADx_CFG = 01<br>PADx_CFG = 10<br>PADx_CFG = 11                                                                                                                                                                                        |          |                      | 220<br>75<br>15<br>3.5 | ns<br>ns<br>ns<br>ns |

| 230               | tf()           | Fall Time GPIO(1:0), ACL,<br>PORTA(3:0), PORTB(2:0),<br>PORTC(3:0)               | CL = 20 pF, fall 7030 % VDDIO<br>PADx_CFG = 00 and GPIO(1:0)<br>PADx_CFG = 01<br>PADx_CFG = 10<br>PADx_CFG = 11                                                                                                                                                                                        |          |                      | 220<br>75<br>15<br>3.5 | ns<br>ns<br>ns<br>ns |

| 231               | tf()           | Fall Time SCL, SDA                                                               | CL = 10100 pF, fall 7030 % VDDIO<br>VDDIO = 2.253.0 V<br>VDDIO = 3.05.5 V                                                                                                                                                                                                                              | 15<br>20 |                      | 150<br>250             | ns<br>ns             |

| PRC F             | Photocurrer    | nt Amplifiers and Comparators                                                    |                                                                                                                                                                                                                                                                                                        |          |                      |                        |                      |

| 306               | fc,r()hi       | Cut-Off Frequency PRC (-3 dB)                                                    |                                                                                                                                                                                                                                                                                                        | 1000     |                      |                        | kHz                  |

|                   | 1              | ent Amplifier                                                                    |                                                                                                                                                                                                                                                                                                        |          |                      |                        | 1                    |

| 501               | fc,a()hi       | Cut-Off Frequency Analog (-3 dB)                                                 |                                                                                                                                                                                                                                                                                                        | 240      |                      |                        | kHz                  |

| 505               | Vv()dc,eff     | Effective DC Signal Level                                                        | LED_CTRL = 1 and LED_CUR = 0 (sum con-<br>trol)<br>Vv()dc,eff = Vv()dc - Vv()d<br>with Vv()d dark signal level                                                                                                                                                                                         | 280      |                      | 480                    | mV                   |

| Analo             | g Output       |                                                                                  |                                                                                                                                                                                                                                                                                                        |          |                      |                        | П                    |

| A01               | Vout()dc       | Output Signal DC Level                                                           | ANA_SEL=00                                                                                                                                                                                                                                                                                             | 48       | 50                   | 52                     | %VDDA                |

| A02               | Vout()ac       | Output Signal AC Amplitude                                                       | ANA_SEL = 00<br>ANA_OS = 0<br>ANA_OS = 1                                                                                                                                                                                                                                                               |          | 1000<br>250          |                        | mV<br>mV             |

| A03               | l()mx          | Permissible Load Current                                                         | ANA_SEL = 00<br>ANA_OS = 0<br>ANA_OS = 1                                                                                                                                                                                                                                                               | -1<br>-6 |                      | 1<br>6                 | mA<br>mA             |

| A04               | C()mx          | Permissible Capacitive Load                                                      | ANA_SEL=00                                                                                                                                                                                                                                                                                             |          |                      | 50                     | pF                   |

| ABZ (             | Generator      |                                                                                  |                                                                                                                                                                                                                                                                                                        |          |                      |                        |                      |

| C01               | AAabs<br>(INL) | Absolute Angle Accuracy<br>(Integral Nonlinearity)                               | Ideal waveform, f()sin $\le$ 60 kHz<br>IPO_FILT1 = 0xEA, IPO_FILT2 = 0x4                                                                                                                                                                                                                               |          | 0.5                  |                        | °e                   |

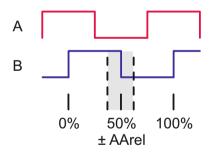

| C02               | AArel<br>(DNL) | Relative Angle Accuracy<br>(Differential Nonlinearity)                           | Ideal waveform<br>IPO_FILT1 = 0xEA, IPO_FILT2 = 0x4<br>ABZ_PER $\leq 2^{SYS}$ _eff x 256, f()sin = 128 Hz<br>ABZ_PER $\leq 2^{SYS}$ _eff x 256, f()sin = 2.56 kHz<br>ABZ_PER $\leq 2^{SYS}$ _eff x 1024, f()sin = 128 Hz<br>ABZ_PER $\leq 2^{SYS}$ _eff x 1024, f()sin = 2.56 kHz<br>see also Figure 1 |          | 15<br>2.5<br>35<br>7 |                        | %<br>%<br>%          |

| C03               | fout()         |                                                                                  | ABZ_MTD = 0x0 (default), f()sin $\leq$ 240 kHz                                                                                                                                                                                                                                                         | 6        |                      |                        | MHz                  |

|                   | Power Contr    |                                                                                  | 1                                                                                                                                                                                                                                                                                                      | -        |                      |                        | 1                    |

| L01               | lop()          | Permissible LED Current                                                          | except startup                                                                                                                                                                                                                                                                                         | 0.5      |                      | 30                     | mA                   |

| L02               | Ictrl()        | Controlled LED Output Current                                                    | refer to Table 145 for details                                                                                                                                                                                                                                                                         |          | 510                  |                        | mA                   |

| L03               | lop()min       | Minimum LED Current                                                              |                                                                                                                                                                                                                                                                                                        |          | 50                   |                        | %lop()               |

Rev F1, Page 11/85

### ELECTRICAL CHARACTERISTICS

| tem    | Symbol       | Parameter                                              | Conditions                                          |            |          | .       | Unit     |

|--------|--------------|--------------------------------------------------------|-----------------------------------------------------|------------|----------|---------|----------|

| No.    |              |                                                        |                                                     | Min.       | Тур.     | Max.    |          |

| L07    | Ic,led       | LED Constant Current                                   | LED_CUR = 0x0                                       | 30         | 40       | 70      | mA       |

|        |              |                                                        | LED_CUR = 0x1                                       | 0          | 0        | 0.1     | m M      |

|        |              |                                                        | LED_CUR = 0x2                                       | 0.75       | 1        | 2.3     | ∣ mA     |

|        |              |                                                        | $LED_CUR = 0x3$                                     | 1.5        | 2        | 4.3     | mA mA    |

|        |              |                                                        | LED_CUR = 0x4<br>LED_CUR = 0x5                      | 3          | 4<br>8   | 8<br>16 | mA<br>mA |

|        |              |                                                        | LED_CUR = 0x6                                       | 12         | 16       | 29      | mA       |

|        |              |                                                        | $LED_CUR = 0x7$                                     | 24         | 32       | 56      | mA       |

| Oscill | ator         | I                                                      | 1                                                   | и          |          |         |          |

| O01    | fosc         | Oscillator Frequency                                   |                                                     | 72         | 80       | 88      | MHz      |

| Power  | 1            | & Voltage Monitoring                                   |                                                     |            |          |         | 0        |

| P01    | VDDAon       | Turn-On Threshold VDDA<br>(power-on release)           | increasing voltage at VDDA                          |            |          | 3.95    | V        |

| P02    | VDDAoff      | Turn-Off Threshold VDDA<br>(power-down reset)          | decreasing voltage at VDDA                          | 3.00       |          |         | V        |

| P03    | VDDAhys      | Threshold Hysteresis VDDA                              | VDDAhys = VDDAon - VDDAoff                          | 200        | 300      | 600     | mV       |

| P04    | VDDIOpor     | Threshold VDDIO for Voltage<br>Regulator<br>(power-on) | increasing voltage at VDDIO                         |            |          | 2.20    | V        |

| P05    | VDDIOon      | Turn-On Threshold VDDIO                                | increasing voltage at VDDIO                         |            |          |         |          |

|        |              | (diagnosis-ok)                                         | VDDIOSEL = 00 (2.5 V)                               |            |          | 2.20    | V        |

|        |              |                                                        | VDDIOSEL = 01 (3.3 V)                               |            |          | 2.95    | V        |

|        |              |                                                        | VDDIOSEL = 10 (5.0 V)                               |            |          | 3.95    | V        |

| P06    | VDDIOoff     | Turn-Off Threshold VDDIO                               | decreasing voltage at VDDIO                         |            |          |         |          |

|        |              | (diagnosis-error)                                      | VDDIOSEL = 00 (2.5 V)                               | 1.3<br>2.2 |          |         | V<br>V   |

|        |              |                                                        | VDDIOSEL = 01 (3.3 V)<br>VDDIOSEL = 10 (5.0 V)      | 3.0        |          |         | V        |

| P07    | VDDIOhys     | Threshold Hysteresis VDDIO                             | VDDIOhys = VDDIOon - VDDIOoff                       | 0.0        |          |         |          |

| FUI    | VDDIOIIys    |                                                        | VDDIOSEL = 00 (2.5 V)                               |            | 250      |         | mV       |

|        |              |                                                        | VDDIOSEL = 01 (3.3 V)                               |            | 200      |         | mV       |

|        |              |                                                        | VDDIOSEL = 10 (5.0 V)                               |            | 250      |         | mV       |

| Linea  | r Regulator  |                                                        |                                                     |            |          |         |          |

| R01    | C(C1V8)      | Recommended Capacity at C1V8                           |                                                     |            | 100      |         | nF       |

| -      | tment Analo  | -                                                      |                                                     |            |          |         |          |

| S01    |              | Minimum Offset Correction                              | COS_OFF(9:0) = 0x3FF and/or<br>SIN_OFF(9:0) = 0x3FF |            |          | -100    | mV       |

| S02    | COROS()mx    | Maximum Offset Correction                              | COS_OFF(9:0) = 0x1FF and/or<br>SIN_OFF(9:0) = 0x1FF | 100        |          |         | mV       |

| S03    | CFA()min     | Minimum Amplitude Correction<br>Factor                 | SC_GAIN = 0x200                                     |            |          | 0.825   |          |

| S04    | CFA()mx      |                                                        | SC_GAIN = 0x1FF                                     | 1.20       | <u> </u> |         |          |

| S05    | CORPH()min   | Minimum Shift of Phase                                 | SC_PHASE(9:0) = 0x1FF                               |            |          | -10     | °e       |

| S06    | CORPH()mx    | Maximum Shift of Phase                                 | SC_PHASE(9:0) = 0x3FF                               | 10         |          |         | °e       |

| Tempe  | erature Sens | sor                                                    |                                                     |            |          |         |          |

| T01    | Trng         | Temperature Sensor Range                               |                                                     | -50        |          | 175     | °C       |

| T02    | Tres         | Temperature Sensor Resolution                          |                                                     |            | 0.1      |         | °C       |

| T03    | Тасс         | Temperature Sensor Accuracy                            | Tj = -40140 °C and after adjustment at<br>iC-Haus   | -3         |          | 3       | °C       |

| Startu | 1            |                                                        |                                                     |            |          |         |          |

| W01    | tstart()     | Startup Time                                           | VDDA > VDDAon                                       |            | 14       |         | ms       |

|        |              |                                                        | VDDIO > VDDIOpor                                    |            |          |         |          |

|        |              | 1                                                      | EEPROM with valid configuration attached to         |            |          |         |          |

HIGH-RESOLUTION REFLECTIVE ABSOLUTE ENCODER

Rev F1, Page 12/85

#### **ELECTRICAL CHARACTERISTICS**

| ltem  | Symbol      | Symbol Parameter                    | Conditions                                                                         |       |                     |      | Unit |

|-------|-------------|-------------------------------------|------------------------------------------------------------------------------------|-------|---------------------|------|------|

| No.   |             |                                     |                                                                                    | Min.  | Тур.                | Max. |      |

| Seria | Interfaces  |                                     |                                                                                    |       |                     |      |      |

| Z01   | fBISS       | Permissible BiSS-Slave<br>Frequency | point-to-point configuration                                                       |       |                     | 20   | MHz  |

|       |             |                                     | bus configuration (chaining multiple chips)                                        |       |                     | 10   | MHz  |

| Z02   | fSSI        | Permissible SSI-Slave Frequency     |                                                                                    |       |                     | 10   | MHz  |

| Z03   | fSPI        | Permissible SPI-Slave Frequency     | point-to-point configuration                                                       |       |                     | 12   | MHz  |

|       |             |                                     | bus configuration (chaining multiple chips), as of $t_{P1}$ and $t_{P3}$           |       |                     |      |      |

|       |             |                                     | 2 chips                                                                            |       |                     | 10   | MHz  |

|       |             |                                     | 3 chips                                                                            |       |                     | 5.88 | MHz  |

|       |             |                                     | 4 chips                                                                            |       |                     | 4.17 | MHz  |

|       |             |                                     | n chips, n $\ge 2$ : $f = \frac{100}{7n-4}$                                        |       |                     | f    | MHz  |

| Z04   | fl2C        | I2C-Master Frequency                | EEPROM attached to SCL/SDA                                                         |       | 220                 | 400  | kHz  |

| Z05   | tsample     |                                     | refer to characteristics in BiSS SLAVE on page 43                                  | 50    | 67                  | 75   | ns   |

| Z06   | tout()adapt | Adaptive Slave Timeout at SLO       | BISS_NTOA = 0                                                                      | 0.075 | t <sub>init</sub> + | 24   | μs   |

|       |             |                                     | refer to timing Figure 4 $t_{init}$ measured as first 1.5 $\cdot$ T(MA) each frame |       | 0.2                 |      |      |

| Z07   | tout()fixed | Fixed Slave Timeout at SLO          | BISS_NTOA = 1                                                                      | 16    | 20                  | 24   | μs   |

|       |             |                                     | refer to timing Figure 4                                                           |       |                     |      |      |

#### **ELECTRICAL CHARACTERISTICS: Diagrams**

Figure 1: Definition of AB duty cycle variation.

Rev F1, Page 13/85

### **OPERATING REQUIREMENTS: Supply Voltages**

| ltem            | Symbol               | Parameter               | Conditions |                          |         | Unit |

|-----------------|----------------------|-------------------------|------------|--------------------------|---------|------|

| No.             |                      |                         |            | Min.                     | Max.    |      |

| Supply Voltages |                      |                         |            |                          |         |      |

| 1001            | t <sub>r,VDDIO</sub> | VDDIO Rise Time         |            | refer to Elec. Char. 005 |         |      |

| 1002            | VDDIO(t)             | Voltage VDDIO at time t |            |                          | VDDA(t) | V    |

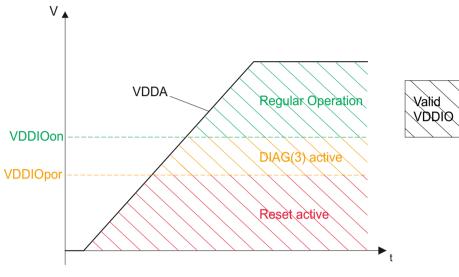

Figure 2: Supply voltages at startup

Rev F1, Page 14/85

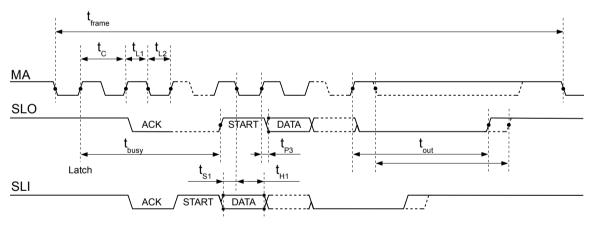

#### **OPERATING REQUIREMENTS: BISS Slave**

| ltem   | Symbol             | Parameter                                                  | Conditions                                                                                                                  |             |                        | Unit                 |

|--------|--------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------|------------------------|----------------------|

| No.    |                    |                                                            |                                                                                                                             | Min.        | Max.                   |                      |

| BiSS p | orotocol           |                                                            |                                                                                                                             |             |                        |                      |

| I101   | t <sub>frame</sub> | Permissible Frame Repetition                               |                                                                                                                             | (*)         | indefinite             |                      |

| I102   | t <sub>C</sub>     | Permissible Clock Period                                   |                                                                                                                             | 50          |                        | ns                   |

| I103   | t <sub>L1</sub>    | Clock Signal hi Level Duration                             |                                                                                                                             | 20          | t <sub>out</sub>       | ns                   |

| I104   | t <sub>L2</sub>    | Clock Signal lo Level Duration                             |                                                                                                                             | 20          | t <sub>out</sub>       | ns                   |

| I105   | t <sub>busy</sub>  | Processing Time with Start Bit Delay                       |                                                                                                                             |             | 5∙t <sub>C</sub>       |                      |

| 1106   | t <sub>P3</sub>    | Propagation Delay: SLO stable after MA lo $\rightarrow$ hi | CL = 20 pF, rise to 70 % VDDIO or fall to 30 %<br>VDDIO<br>PADx_CFG = 00<br>PADx_CFG = 01<br>PADx_CFG = 10<br>PADx_CFG = 11 |             | 400<br>150<br>60<br>35 | ns<br>ns<br>ns<br>ns |

| I107   | t <sub>out</sub>   | Adaptive Slave Timeout                                     |                                                                                                                             | refer to El | ec. Char. Z06          |                      |

| 1108   | t <sub>S1</sub>    | Setup Time: SLI stable before MA hi $\rightarrow$ lo       |                                                                                                                             | 5           |                        | ns                   |

| I109   | t <sub>H1</sub>    | Hold Time: SLI stable after MA hi $\rightarrow$ lo         |                                                                                                                             | 10          |                        | ns                   |

(\*) Allow tout to elapse.

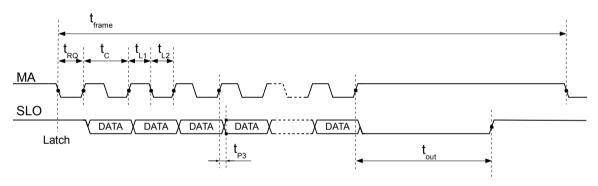

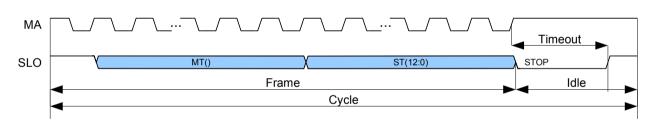

#### Figure 3: BiSS timing

Figure 4: BiSS slave timeout

Rev F1, Page 15/85

#### **OPERATING REQUIREMENTS: SSI Slave**

| Item   | Symbol             | Parameter                                                  | Conditions                                                                                                 |              |                  | Unit           |

|--------|--------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------|------------------|----------------|

| No.    |                    |                                                            |                                                                                                            | Min.         | Max.             |                |

| SSI pr | otocol             |                                                            | ·                                                                                                          |              |                  |                |

| 1201   | t <sub>frame</sub> | Permissible Frame Repetition                               |                                                                                                            | (*)          | indefinite       |                |

| 1202   | t <sub>C</sub>     | Permissible Clock Period                                   |                                                                                                            | 100          |                  | ns             |

| 1203   | t <sub>L1</sub>    | Clock Signal hi Level Duration                             |                                                                                                            | 25           | t <sub>out</sub> | ns             |

| 1204   | t <sub>L2</sub>    | Clock Signal lo Level Duration                             |                                                                                                            | 25           | t <sub>out</sub> | ns             |

| 1205   | t <sub>RQ</sub>    | REQ Signal lo Level Duration                               |                                                                                                            | 50           |                  | ns             |

| 1206   | t <sub>P3</sub>    | Propagation Delay: SLO stable after MA lo $\rightarrow$ hi | CL = 20 pF, rise to 70 % VDDIO or fall to 30 %<br>VDDIO<br>PADx_CFG = 00<br>PADx_CFG = 01<br>PADx_CFG = 10 |              | 400<br>150<br>60 | ns<br>ns<br>ns |

|        |                    |                                                            | PADx_CFG = 11                                                                                              |              | 35               | ns             |

| 1207   | t <sub>out</sub>   | Adaptive Slave Timeout                                     |                                                                                                            | refer to Ele | ec. Char. Z06    |                |

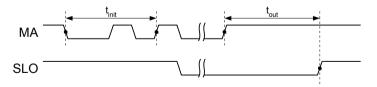

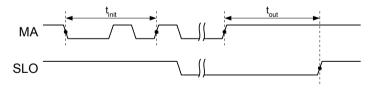

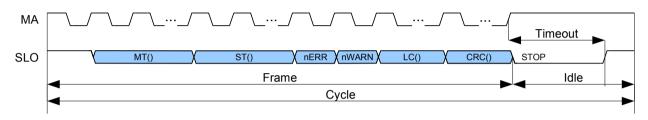

Figure 5: SSI timing

Figure 6: SSI slave timeout

HIGH-RESOLUTION REFLECTIVE ABSOLUTE ENCODER

Rev F1, Page 16/85

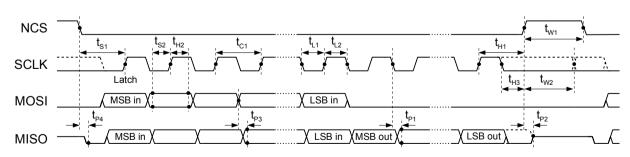

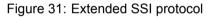

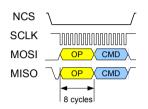

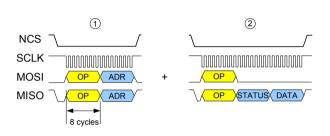

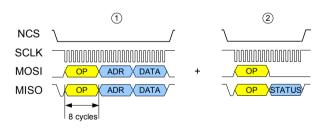

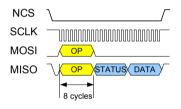

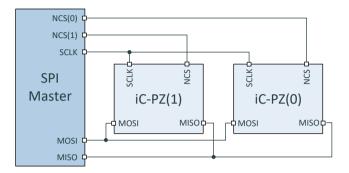

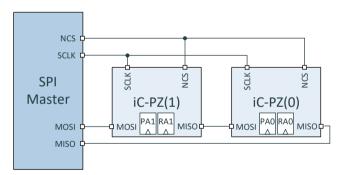

### **OPERATING REQUIREMENTS: SPI Slave**

| ltem<br>No. | Symbol          | Parameter                                                              | Conditions                                                                                                                  | Min.  | Max.                   | Unit                 |

|-------------|-----------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------|------------------------|----------------------|

| SPI pr      | otocol          | 1                                                                      |                                                                                                                             |       |                        |                      |

| 1301        | t <sub>C1</sub> | Permissible Clock Cycle Time                                           |                                                                                                                             | 83.33 |                        | ns                   |

| 1302        | t <sub>L1</sub> | Clock Signal lo Level Duration                                         |                                                                                                                             | 30    |                        | ns                   |

| 1303        | t <sub>L2</sub> | Clock Signal hi Level Duration                                         |                                                                                                                             | 30    |                        | ns                   |

| 1304        | t <sub>S1</sub> | Setup Time: NCS lo before SCLK lo $\rightarrow$ hi                     |                                                                                                                             | 41.67 |                        | ns                   |

| 1305        | t <sub>H1</sub> | Hold Time: NCS lo after SCLK lo $\rightarrow$ hi                       | valid for SPI mode 3                                                                                                        | 41.67 |                        | ns                   |

| 1306        | t <sub>H3</sub> | Hold Time: NCS lo after SCLK hi $\rightarrow$ lo                       | valid for SPI mode 0                                                                                                        | 41.67 |                        | ns                   |

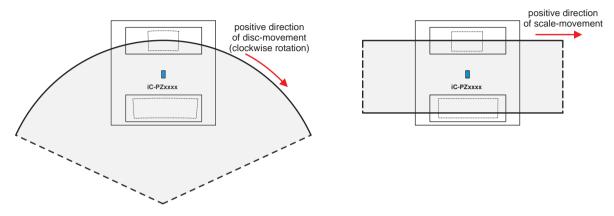

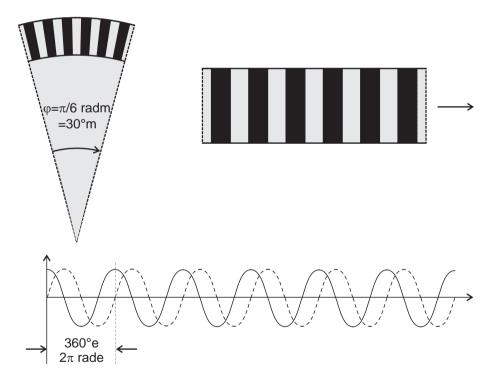

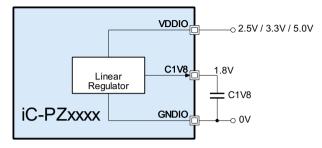

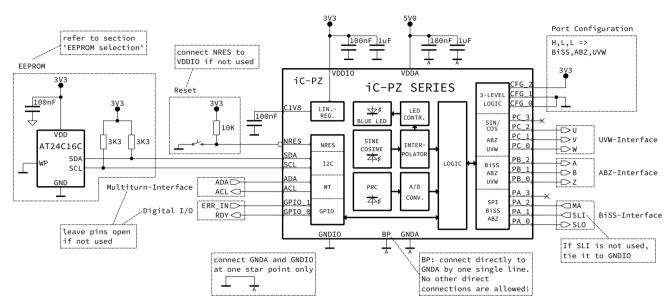

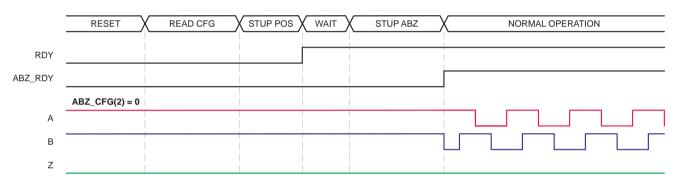

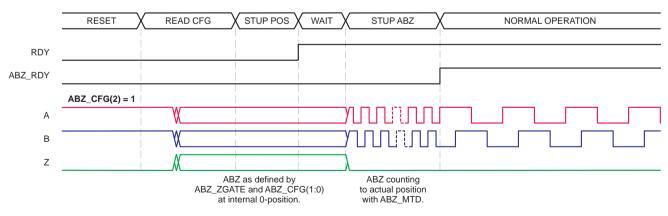

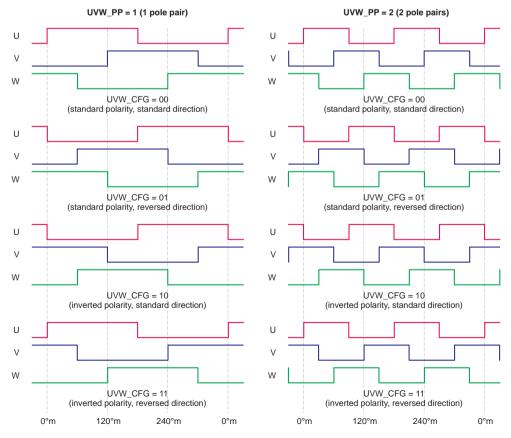

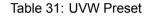

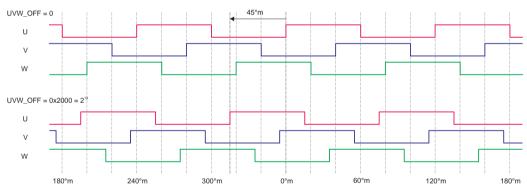

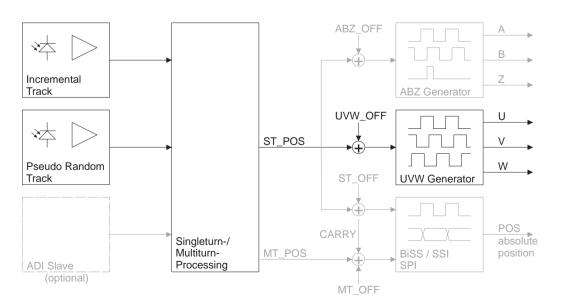

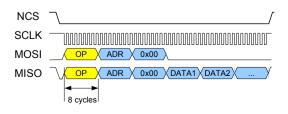

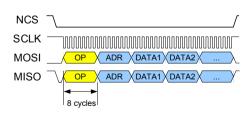

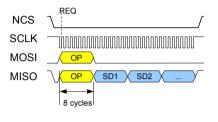

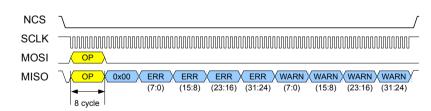

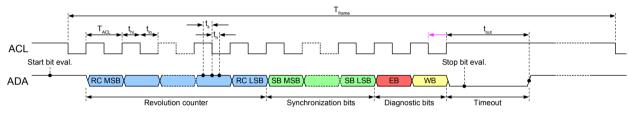

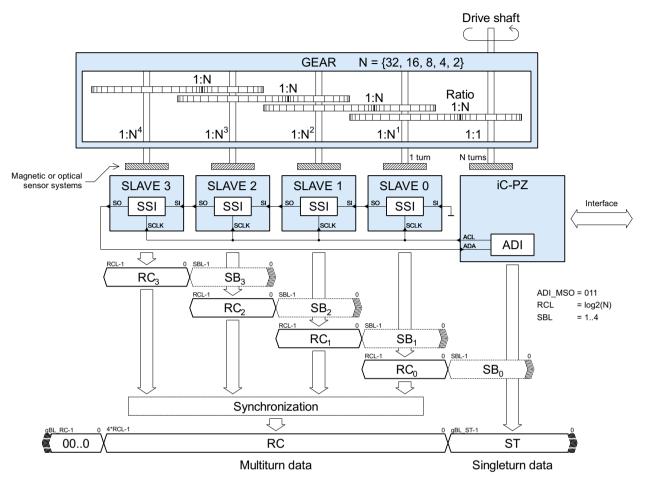

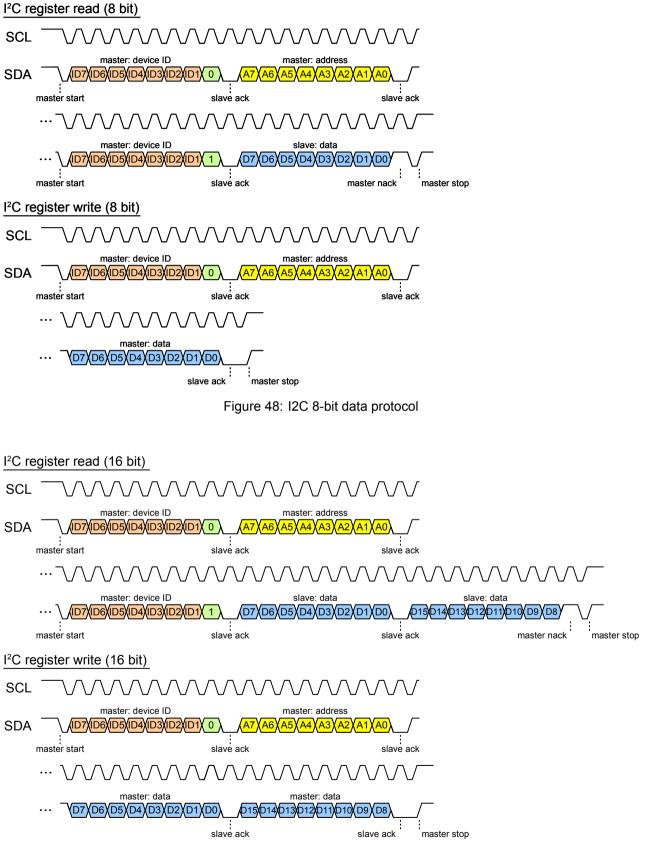

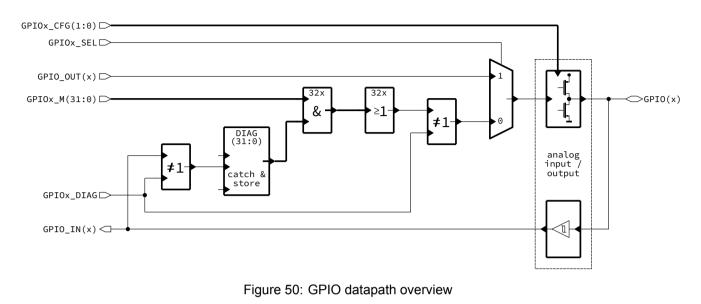

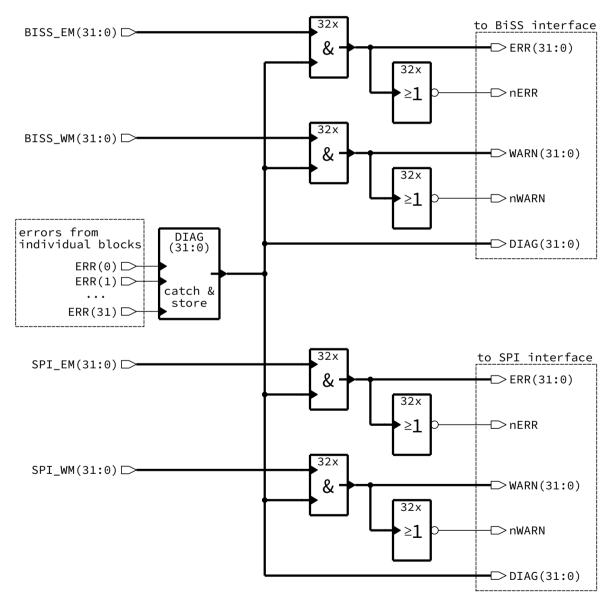

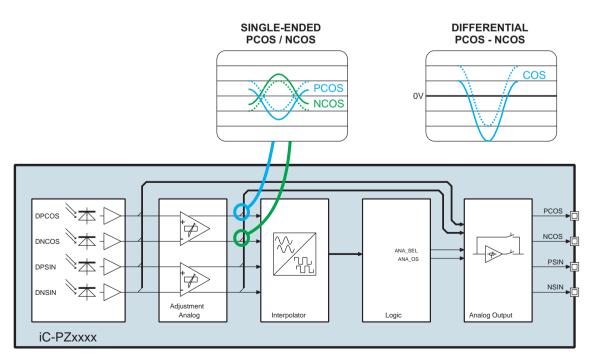

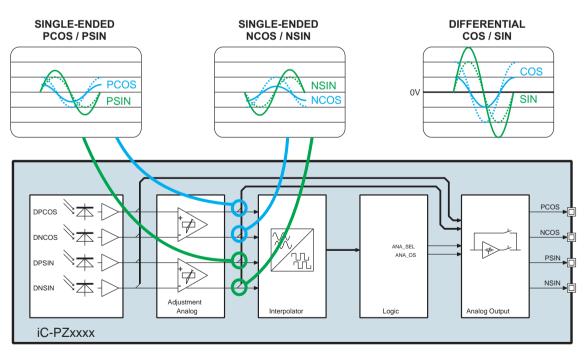

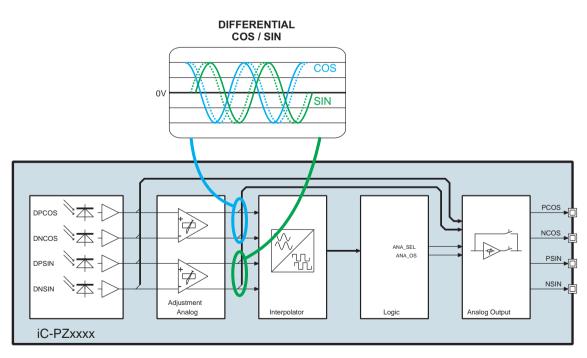

| 1307        | t <sub>W2</sub> | Wait Time:<br>NCS hi before SCLK change                                |                                                                                                                             | 200   |                        | ns                   |