## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 1/36

#### **FEATURES**

- ♦ BiSS Interface slave

- ♦ Full BiSS protocol support

- ♦ Two data channel configurable

- ♦ Three slave IDs occupiable

- ♦ Single-cycle data buffer of 64 byte organized in multiple banks for simultaneous access

- ♦ Built-in control communication

- ♦ RS422 line driver/receiver for BiSS/SSI point-to-point network

- ♦ BiSS bus structure capable

- ♦ SPI slave interface for sensor data provided by microcontroller

- ◆ Fast Sensor interface for direct sensor data provided by an SPI slave device

- ♦ BiSS safety related features: Two data channels for Control and Safety Position Word, 6/16 bit CRC + CRC start value

- ♦ BiSS timeout: adaptive, 2 µs, 20 µs

- ♦ SSI protocol support

- ♦ Operation from 3.0 V to 5.5 V

- ♦ Operating temperature range of -40° C to +125° C

- ♦ Space-saving 16-pin QFN package

#### **APPLICATIONS**

- ♦ BiSS slave implementation

- Multiple sensor devices

- ♦ Encoder

- ♦ Condition monitoring extension

- Diagnosis extension

- ♦ Torque sensor

- Acceleration sensor

- ♦ Inclinometer

- Safety light curtain

## PACKAGES

16-pin QFN 3 mm x 3 mm RoHS compliant

### SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 2/36

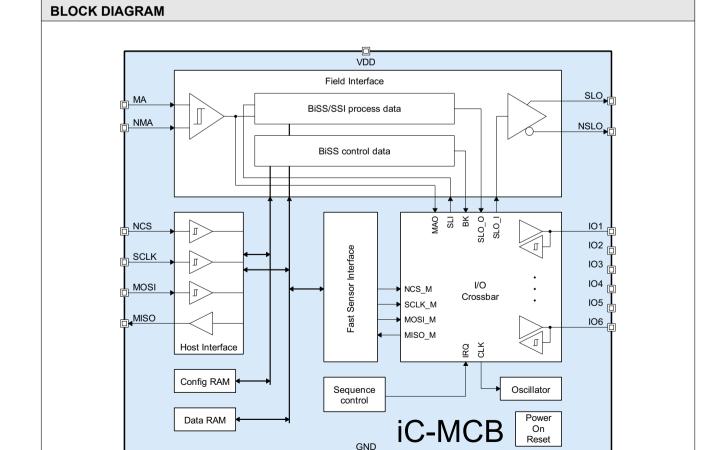

#### **DESCRIPTION**

iC-MCB is a BiSS slave bridge component suitable to implement BiSS slave functionality into any device and platform.

It is designed for BiSS sensor implementations and also enables downgrading to SSI operation. Full BiSS C protocol functionality including single-cycle data (SCD) for sensors (SCDS) and control communication (e.g. for register accesses). Time-critical protocol specific actions are handled directly by the iC-MCB.

Besides the BiSS/SSI field interface, iC-MCB provides

- · a Host Interface (SPI Slave Interface)

- a Fast Sensor Interface (e.g. SPI Master Interface)

Typically, the host interface is used to configure iC-MCB on start-up, support iC-MCB during BiSS control communication and provide sensor data. However, iC-MCB can also operate as a master to automatically access various sensors (e.g. SPI sensors) directly by its Fast Sensor Interface at the I/O crossbar. To this end, the Fast Sensor Interface is fully configurable including signals, phase, polarity, clock frequency, data lengths and header.

With the integrated RS422 transceiver iC-MCB is perfectly equipped for BiSS point-to-point encoder applications with a maximum clock rate of 10 MHz. BiSS bus structures are also supported by enabling data input pin SLI and clock output pin MAO at the I/O crossbar.

## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 3/36

#### **PACKAGING INFORMATION**

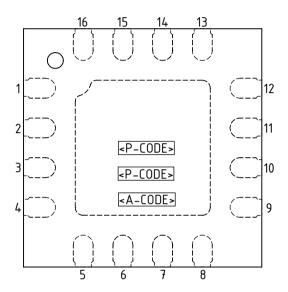

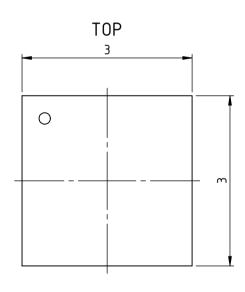

### **PIN CONFIGURATION** QFN16-3x3 (3 mm x 3 mm x 0.9 mm) (according to JEDEC Standard MO-220)

#### **PIN FUNCTIONS** Name Function No.

| υ. | INAIIIE | runction                  |

|----|---------|---------------------------|

| 1  | MISO    | SPI Serial Data Output    |

| 2  | NCS     | SPI Chip Select Input     |

| 3  | SCLK    | SPI Clock Input           |

| 4  | MOSI    | SPI Serial Data Input     |

| 5  | IO1     | Digital Port Input/Output |

| 6  | 102     | Digital Port Input/Output |

Digital Port Input/Output 7 103 8 104 Digital Port Input/Output 9 105 Digital Port Input/Output

10 106 Digital Port Input/Output

11 GND Ground

12 VDD +3.0 V to +5.5 V Supply Voltage 13 NSLO BiSS Data Line Output (inverted)

14 SLO **BiSS Data Line Output** 15 MA **BiSS Clock Line Input**

BiSS Clock Line Input (inverted) 16 NMA

Backside Paddle 1) ΒP

IC top marking: <P-CODE> = product code, <A-CODE> = assembly code (subject to changes);

<sup>1)</sup> Connecting the backside paddle is recommended by a single link to GND. A current flow across the paddle is not permissible.

## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 4/36

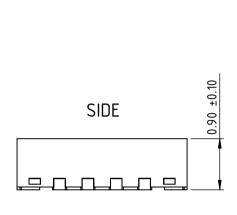

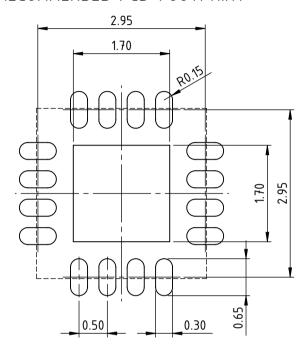

### PACKAGE DIMENSIONS QFN16 3 mm x 3 mm x 0.9 mm

## RECOMMENDED PCB-FOOTPRINT

All dimensions given in mm. Tolerances of form and position according to JEDEC MO-220.

drb\_qfn16-3x3-1\_pack\_1, 15:1

## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 5/36

### **ABSOLUTE MAXIMUM RATINGS**

Beyond these values damage may occur; device operation is not guaranteed.

| Item | Symbol | Parameter                                                      | Conditions                           |      |      | Unit |

|------|--------|----------------------------------------------------------------|--------------------------------------|------|------|------|

| No.  |        |                                                                |                                      | Min. | Max. |      |

| G001 | V(VDD) | Voltage at VDD                                                 |                                      | -0.3 | 6    | V    |

| G002 | V()    | Voltage at MISO, NCS, SCLK, MOSI, IO1, IO2, IO3, IO4, IO5, IO6 | V() < V(VDD) + 0.3 V                 | -0.3 | 6    | V    |

| G003 | V()    | Voltage at SLO, NSLO                                           |                                      | -0.3 | 6    | V    |

| G004 | V()    | Voltage at MA, NMA                                             |                                      | -10  | 10   | V    |

| G005 | I(VDD) | Current in VDD                                                 |                                      | -100 | 150  | mA   |

| G006 | Vd()   | ESD Susceptibility at all pins                                 | HBM 100 pF discharged through 1.5 kΩ |      | 2    | kV   |

| G007 | Tj     | Junction Temperature                                           |                                      | -40  | 150  | °C   |

| G008 | Ts     | Storage Temperature Range                                      |                                      | -40  | 150  | °C   |

### THERMAL DATA

| Item | tem Symbol Parameter C |                                     | Conditions                                                                           |      | Unit |      |     |

|------|------------------------|-------------------------------------|--------------------------------------------------------------------------------------|------|------|------|-----|

| No.  |                        |                                     |                                                                                      | Min. | Тур. | Max. |     |

| T01  | Та                     | Operating Ambient Temperature Range | package QFN16-3x3                                                                    | -40  |      | 125  | °C  |

| T02  | Rthja                  | •                                   | QFN16-3x3 surface mounted to PCB according to JEDEC 51 thermal measurement standards |      | 45   |      | K/W |

## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 6/36

## **ELECTRICAL CHARACTERISTICS**

Operating Conditions: VDD =  $3.0 \dots 5.5 \text{ V}$ ,  $T_j = -40 \dots 125 \,^{\circ}\text{C}$ , unless otherwise noted.

| Item<br>No. | Symbol              | Parameter                                                                     | Conditions                                                                                                                      | Min.          | Тур.                      | Max.           | Unit           |

|-------------|---------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------|----------------|----------------|

| Gene        | ral                 | 1                                                                             | ı                                                                                                                               |               |                           |                |                |

| 001         | VDD                 | Permissible Supply Voltage                                                    |                                                                                                                                 | 3.0           |                           | 5.5            | V              |

| 002         | I(VDD)              | Supply Current                                                                | without load                                                                                                                    |               | 5                         | 8              | mA             |

| 003         | Vc()hi              | Clamp Voltage hi at MISO, NCS,<br>SCLK, MOSI, IO1, IO2, IO3, IO4,<br>IO5, IO6 | Vc()hi = V() - VDD; I() = 1 mA                                                                                                  | 0.4           |                           | 1.5            | V              |

| 004         | Vc()lo              | Clamp Voltage Io at MISO, NCS,<br>SCLK, MOSI, IO1, IO2, IO3, IO4,<br>IO5, IO6 | I() = -1 mA                                                                                                                     | -1.5          |                           | -0.3           | V              |

| Field       | Interface: E        | BiSS/SSI RS422 Line Driver Outpu                                              | its SLO, NSLO                                                                                                                   |               |                           |                | "              |

| 201         | Vs()hi              | Saturation Voltage hi                                                         | Vs() = VDD - V(); I() = -20 mA                                                                                                  |               |                           | 500            | mV             |

| 202         | Vs()lo              | Saturation Voltage lo                                                         | I() = 20 mA                                                                                                                     |               |                           | 400            | mV             |

| 203         | lsc()hi             | Short-circuit Current hi                                                      | V() = 0 V                                                                                                                       | -60           | -30                       | -20            | mA             |

| 204         | lsc()lo             | Short-circuit Current lo                                                      | V() = VDD                                                                                                                       | 20            | 45                        | 90             | mA             |

| Field       |                     | BiSS/SSI RS422 Line Receiver MA                                               | · ·                                                                                                                             |               | 1                         |                | 11             |

| 210         | Vin()               | Permissible Input Voltage                                                     |                                                                                                                                 | -10           |                           | 10             | V              |

| 211         | Vcm()               | Input Common Mode Voltage                                                     |                                                                                                                                 | -7            |                           | 7              | V              |

| 212         | Vdiff()             | Differential Input Voltage                                                    | Vdiff() = V(MA) - V(NMA)                                                                                                        | -12           |                           | 12             | V              |

| 213         | Rin()               | Input Resistance                                                              | MA vs. GND, NMA vs. GND                                                                                                         | 4             |                           |                | kΩ             |

| 214         | Vt()diff            | Differential Input Threshold                                                  | Vt(MA)diff = V(MA) - V(NMA)<br>$t_C = 334 \text{ ns } (f_C = 3 \text{ MHz})$<br>$t_C = 100 \text{ ns } (f_C = 10 \text{ MHz})$  | -200<br>-400  |                           | 200<br>400     | mV<br>mV       |

| 215         | Vt()hys             | Differential Input Hysteresis                                                 | Vt()hys = V(MA) - V(NMA)                                                                                                        | 5             | 60                        | 200            | mV             |

| 216         | Vt()hi              | Input Threshold Voltage hi at MA                                              | ESE = 1                                                                                                                         |               |                           | 70             | %VDD           |

| 217         | Vt()lo              | Input Threshold Voltage lo at MA                                              | ESE = 1                                                                                                                         | 30            |                           |                | %VDD           |

| Field       | Interface: E        | BISS/SSI Timing                                                               | ,                                                                                                                               | "             | ,                         |                | "              |

| 220         | fclk()              | Permissible Clock Frequency at MA                                             | SSI protocol<br>BiSS C protocol                                                                                                 |               |                           | 4<br>10        | MHz<br>MHz     |

| 221         | tr()                | Rise Time hi at SLO, NSLO                                                     | RL = 100 Ω to GND, rise 10 % to 90 %                                                                                            |               |                           | 20             | ns             |

| 222         | tf()                | Fall Time lo at SLO, NSLO                                                     | RL = 100 Ω to VDD, fall 90 % to 10 %                                                                                            |               |                           | 20             | ns             |

| 223         | t <sub>P</sub> ()   | Output Propagation Delay at SLO                                               | versus clock edge MA, ESE = 1;<br>versus clock edge MA, ESE = 0;<br>versus clock edge MAO via IOx;<br>refers to timing Figure 1 | 0<br>0<br>-10 |                           | 40<br>75<br>10 | ns<br>ns<br>ns |

| 224         | t <sub>out</sub> () | Slave Timeout at SLO                                                          | adaptive (NTOA = 0);                                                                                                            | 2/fosc        |                           | 375<br>/fosc   |                |

|             |                     |                                                                               | short (NTOA = 1, TOS = 1);                                                                                                      |               | 30/fosc                   |                |                |

|             |                     |                                                                               | long (NTOA = 1, TOS = 0);                                                                                                       |               | 375<br>/fosc              |                |                |

| 225         | T <sub>CLK</sub>    | Period of BiSS Timeout Sampling Clock                                         | refers to Characteristics in<br>BiSS C Protocol Description                                                                     |               | 1.33<br>/f <sub>OSC</sub> |                |                |

## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 7/36

## **ELECTRICAL CHARACTERISTICS**

Operating Conditions: VDD = 3.0 ... 5.5 V, T<sub>i</sub> = -40 ... 125 °C, unless otherwise noted.

| ltem<br>No. | Symbol              | Parameter                                   | Conditions                                                                                                         | Min. | Тур. | Max.     | Unit     |

|-------------|---------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|------|----------|----------|

|             | nterface SP         | PI Slave NCS, SCLK, MOSI, MISC              | 0                                                                                                                  |      | -71- |          |          |

| 301         | Vs()hi              | Saturation Voltage hi at MISO               | Vs() = VDD - V(); I() = -1.6 mA                                                                                    |      |      | 0.4      | V        |

| 302         | Vs()lo              | Saturation Voltage lo at MISO               | I() = -1.6 mA                                                                                                      |      |      | 0.4      | V        |

| 303         | tr()                | Rise Time at MISO                           | CL = 50pf<br>VDD = 3.0 3.6 V, rise 10 % to 70 %<br>VDD = 4.5 5.5 V, rise 10 % to 70 %                              |      |      | 35<br>25 | ns<br>ns |

| 304         | tf()                | Fall Time at MISO                           | CL = 50pf<br>VDD = 3.0 3.6 V, fall 90 % to 0.8 V<br>VDD = 4.5 5.5 V, fall 10 % to 0,8 V                            |      |      | 45<br>35 | ns<br>ns |

| 305         | Vt()hi              | Threshold Voltage hi at NCS, SCLK, MOSI     |                                                                                                                    |      |      | 70       | %VDD     |

| 306         | Vt()lo              | Threshold Voltage lo at NCS, SCLK, MOSI     |                                                                                                                    | 30   |      |          | %VDD     |

| 307         | Vt()hys             | Threshold Hysteresis at NCS, SCLK, MOSI     |                                                                                                                    | 200  |      |          | mV       |

| 308         | lpu()               | Pull-up Current at NCS                      | V() = 0 VVDD - 1 V                                                                                                 | -70  |      | -2       | μA       |

| 309         | lpd()               | Pull-down Current at SCLK, MOSI             | V() = 1 VVDD                                                                                                       | 2    |      | 80       | μА       |

| 310         | t <sub>P1</sub> ()  | Output Propagation Delay at MISO            | CL = 50pf, MISO = 0.5*VDD after SCLK hi $\rightarrow$ lo refers to timing Figure 3 VDD = 3.0 3.6 V VDD = 4.5 5.5 V |      |      | 40<br>25 | ns<br>ns |

| Oscill      | ator                |                                             |                                                                                                                    |      |      |          |          |

| 401         | f <sub>osc</sub>    | Internal Oscillator Frequency               |                                                                                                                    | 12   | 20   | 28       | MHz      |

| 402         | f <sub>osc_in</sub> | External Oscillator Frequency               | Input at I/O Crossbar (CB_CLK = 1)                                                                                 | 12   |      | 18       | MHz      |

| Powe        | r-On Reset          |                                             |                                                                                                                    |      |      |          |          |

| 501         | VDDon               | VDD Turn-on Threshold                       | increasing voltage at VDD vs. GND                                                                                  | 1.5  |      | 2.9      | V        |

| 502         | VDDoff              | VDD Turn-off Threshold (undervoltage reset) | decreasing voltage at VDD vs. GND                                                                                  | 1.2  |      | 2.7      | V        |

| 503         | VDDhys              | VDD Hysteresis                              | VDDhys = VDDon - VDDoff                                                                                            | 200  |      |          | mV       |

| I/O Cr      | ossbar: IO1         | I, IO2, IO3, IO4, IO5, IO6                  |                                                                                                                    |      |      |          |          |

| 601         | Vs()hi              | Saturation Voltage hi                       | Vs() = VDD - V(); I() = -1.6 mA                                                                                    |      |      | 0.4      | V        |

| 602         | Vs()lo              | Saturation Voltage lo                       | I() = -1.6 mA                                                                                                      |      |      | 0.4      | V        |

| 603         | tr()                | Rise Time                                   | CL = 50pf<br>VDD = 3.0 3.6 V, rise 10 % to 70 %<br>VDD = 4.5 5.5 V, rise 10 % to 70 %                              |      |      | 35<br>25 | ns<br>ns |

| 604         | tf()                | Fall Time                                   | CL = 50pf<br>VDD = 3.0 3.6 V, fall 90 % to 0.8 V<br>VDD = 4.5 5.5 V, fall 10 % to 0,8 V                            |      |      | 45<br>35 | ns<br>ns |

| 605         | Vt()hi              | Threshold Voltage hi                        |                                                                                                                    |      |      | 70       | %VDD     |

| 606         | Vt()Io              | Threshold Voltage lo                        |                                                                                                                    | 30   |      |          | %VDD     |

| 607         | Vt()hys             | Threshold Hysteresis                        |                                                                                                                    | 200  |      |          | mV       |

| 608         | lpd()               | Pull-down Current                           | V() = 1 VVDD                                                                                                       | 2    |      | 80       | μA       |

## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 8/36

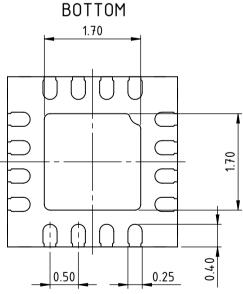

### **OPERATING REQUIREMENTS: Field Interface BiSS**

Operating Conditions: VDD = 3.0 ... 5.5 V, T<sub>i</sub> = -40 ... 125 °C, unless otherwise noted.

| Item | Symbol             | Parameter                      | Conditions                                                                                                        |                          |                  | Unit           |

|------|--------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------|------------------|----------------|

| No.  | -                  |                                |                                                                                                                   | Min.                     | Max.             |                |

| 1001 | t <sub>Cycle</sub> | Permissible Frame Repetition   |                                                                                                                   | *                        | indefinite       |                |

| 1002 | t <sub>busy</sub>  | Processing Time                | data available (asynchronous operation);<br>Note, other modes delay data availability time<br>(refer to Table 10) | 2·t <sub>C</sub>         | 500 ns           |                |

| 1003 | busy_s             | Additional Start Bit Delay     | ACQMODE = 1 or ENFSI = 1                                                                                          |                          | 1                | t <sub>C</sub> |

| 1004 | t <sub>C</sub>     | Permissible Clock Period       |                                                                                                                   | 90                       |                  | ns             |

| 1005 | t <sub>L1</sub>    | Clock Signal hi Level Duration |                                                                                                                   | 45                       | t <sub>out</sub> | ns             |

| 1006 | t <sub>L2</sub>    | Clock Signal lo Level Duration |                                                                                                                   | 45                       | t <sub>out</sub> | ns             |

| 1007 | t <sub>P</sub>     | Output Propagation Delay       |                                                                                                                   | refer to Elec. Char. 223 |                  |                |

| 1008 | t <sub>TO</sub>    | Slave Timeout at SLO           | depending on NTOA and TOS                                                                                         | refer to Elec. Char. 224 |                  |                |

| 1009 | t <sub>Wait</sub>  | Wait Time                      |                                                                                                                   | 500                      |                  | ns             |

<sup>\*</sup>Allow  $t_{out}$  to elapse.

Figure 1: BiSS Protocol Timing

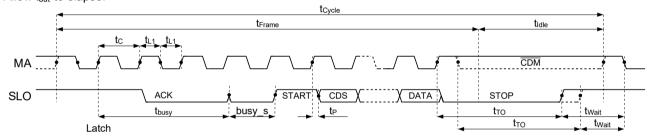

## **OPERATING REQUIREMENTS: Field Interface SSI**

Operating Conditions: VDD = 3.0...5.5 V,  $T_i$  = -40 ... 125 °C, unless otherwise noted.

| Item | Symbol             | Parameter                      | Conditions             |              |                  | Unit |

|------|--------------------|--------------------------------|------------------------|--------------|------------------|------|

| No.  |                    |                                |                        | Min.         | Max.             |      |

| I101 | t <sub>Cycle</sub> | Permissible Frame Repetition   |                        | *            | indefinite       |      |

| I102 | t <sub>C</sub>     | Permissible Clock Period       |                        | 250          |                  | ns   |

| I103 | t <sub>L1</sub>    | Clock Signal hi Level Duration |                        | 45           | t <sub>out</sub> | ns   |

| I104 | t <sub>L2</sub>    | Clock Signal lo Level Duration |                        | 45           | t <sub>out</sub> | ns   |

| I105 | t <sub>RQ</sub>    | REQ Signal lo Level Duration   | ACQMODE = 0, ENFSI = 0 | 45           | t <sub>out</sub> | ns   |

| I106 | t <sub>P</sub>     | Output Propagation Delay       |                        | refer to Ele | ec. Char. 223    |      |

| I107 | t <sub>TO</sub>    | Slave Timeout at SLO           | depending on TOS       | refer to Ele | ec. Char. 224    |      |

| 1108 | t <sub>Wait</sub>  | Wait Time                      |                        | 500          |                  | ns   |

<sup>\*</sup>Allow tout to elapse.

Figure 2: SSI Protocol Timing

## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 9/36

## **OPERATING REQUIREMENTS: Host Interface SPI Slave**

Operating Conditions: VDD = 3.0...5.5 V,  $T_j$  = -40 ... 125 °C, unless otherwise noted.

| Item | Symbol          | Parameter                                                              | Conditions |              |               | Unit |

|------|-----------------|------------------------------------------------------------------------|------------|--------------|---------------|------|

| No.  | -               |                                                                        |            | Min.         | Max.          |      |

| 1201 | t <sub>C</sub>  | Permissible Clock Period                                               |            | 50           |               | ns   |

| 1202 | t <sub>L1</sub> | Clock Signal lo Level Duration                                         |            | 25           |               | ns   |

| 1203 | t <sub>L2</sub> | Clock Signal hi Level Duration                                         |            | 25           |               | ns   |

| 1204 | t <sub>H1</sub> | Hold Time: NCS lo after SCLK lo $\rightarrow$ hi                       |            | 50           |               | ns   |

| 1205 | t <sub>H2</sub> | Hold Time: MOSI stable after SCLK $lo \rightarrow hi$                  |            | 20           |               | ns   |

| 1206 | t <sub>S1</sub> | Setup Time: NCS lo before SCLK lo $\rightarrow$ hi                     |            | 25           |               | ns   |

| 1207 | t <sub>S2</sub> | Setup Time: MOSI stable before SCLK lo $\rightarrow$ hi                |            | 20           |               | ns   |

| 1208 | t <sub>P1</sub> | Propagation Delay:<br>MISO stable after SCLK hi → lo                   |            | refer to Ele | ec. Char. 310 |      |

| 1209 | t <sub>P2</sub> | Propagation Delay: MISO hi impedance after NCS lo $\rightarrow$ hi     |            |              | 50            | ns   |

| I210 | t <sub>W</sub>  | Wait Time: between NCS lo $\rightarrow$ hi and NCS hi $\rightarrow$ lo |            | 250          |               | ns   |

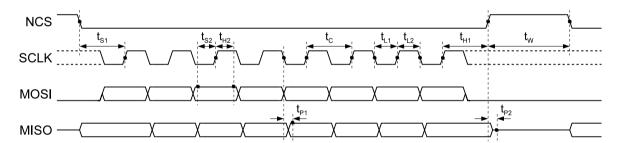

Figure 3: SPI Protocol Timing

GRAY1:

RSSI:

Binary to Gray conversion

SSI ring operation

## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 10/36

### **CONFIGURATION PARAMETERS**

| STARTUP AN                                                          | D OPERATION Page 13                                                                                                                                                                                                                       | HOST INTER                                                                   | FACE: SPI SLAVE Page 19                                                                                                                                                                                                          |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHPREL:<br>CFGOK:<br>ACQMODE:<br>BANKSW:<br>USDST:                  | Chip release Tag configuration data as valid Acquisition mode Bank switch Activity on missing sensor data                                                                                                                                 | CVALID:<br>IVALID:<br>CONFIRM:<br>RDATA:                                     | Control valid indication Valid indication for BiSS commands Confirmation for BiSS register access Register access transfer byte                                                                                                  |

|                                                                     |                                                                                                                                                                                                                                           | <b>FAST SENSO</b>                                                            | R INTERFACE: SPI MASTER Page 29                                                                                                                                                                                                  |

| FIELD INTERF                                                        | FACE: General                                                                                                                                                                                                                             | ENFSI:<br>DLFSI:                                                             | Enable Fast Sensor Interface Data length Fast Sensor Interface                                                                                                                                                                   |

| FIELD INTER                                                         | FACE: BiSS Page 15                                                                                                                                                                                                                        | HEADL:<br>STAFSI:                                                            | SPI request header length Observe start bit from sensor                                                                                                                                                                          |

| BUSY: DLEN1: ENDC1: CPOLY1: CSTART1: DLEN2: ENDC2: CPOLY2: CSTART2: | Minimum start bit delay Data length SCD 1 Enable data channel 1 CRC polynomial data channel 1 CRC start value for data channel 1 Data length SCD 2 Enable data channel 2 CRC polynomial data channel 2 CRC start value for data channel 2 | IDLE:<br>CPOL:<br>CPHA:<br>CLKDIV:<br>HEADER:<br>G2B:<br>REQ_FT:<br>OSCDIV2: | Idle state at MOSI SPI communication protocol polarity SPI communication protocol phase SPI clock divider SPI request header Gray to binary conversion for sensor data BiSS request feedthrough Oscillator Frequency divide by 2 |

| ASID:<br>CMD01DI:                                                   | Request an additional Slave ID BiSS Command 0/1 Control                                                                                                                                                                                   | I/O CROSSBA                                                                  | <b>AR</b> Page 31                                                                                                                                                                                                                |

| CMD2EN:<br>REGPROT:                                                 | BiSS Command 2 Control Enable register protection                                                                                                                                                                                         | CB_FSI:<br>CB_CLK:<br>CB_IRQ:                                                | Configuration Fast Sensor Interface Input for external clock oscillator Interrupt request output                                                                                                                                 |

| FIELD INTER                                                         | FACE: SSI Page 18                                                                                                                                                                                                                         | CB_MAO:                                                                      | BiSS MA clock output                                                                                                                                                                                                             |

| ENSSI:<br>NTOA:<br>TOS:                                             | Protocol selection Disable adaptive timeout Shorten timeout sensor data                                                                                                                                                                   | CB_SLI:<br>CB_SLO:                                                           | BiSS Slave input SLI<br>BiSS Slave output SLO                                                                                                                                                                                    |

## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 11/36

## **REGISTER MAP (HOST INTERFACE)**

| DATA R | DATA RAM                                         |         |                 |                  |                  |                   |        |       |  |  |  |

|--------|--------------------------------------------------|---------|-----------------|------------------|------------------|-------------------|--------|-------|--|--|--|

| Addr   | Bit 7                                            | Bit 6   | Bit 5           | Bit 4            | Bit 3            | Bit 2             | Bit 1  | Bit 0 |  |  |  |

| 0x00   | 0x00 Single-Cycle Data for data channels 1 and 2 |         |                 |                  |                  |                   |        |       |  |  |  |

| 0x3F   |                                                  | (The Da | nta RAM is sepa | rated into 4 men | nory banks of eq | ual size, if BANk | (SW=1) |       |  |  |  |

Table 1: Data RAM (Access via SPI)

| CONFIC   | SURATION F            | RAM         |         |                   |                                  |          |             |          |  |

|----------|-----------------------|-------------|---------|-------------------|----------------------------------|----------|-------------|----------|--|

| Addr     | Bit 7                 | Bit 6       | Bit 5   | Bit 4             | Bit 3                            | Bit 2    | Bit 1       | Bit 0    |  |

| FIELD IN | ITERFACE: B           | iSS/SSI     | 1       | 1                 |                                  | '        | 1           |          |  |

| 0x40     | GRAY1                 | ENDC1       |         |                   | DLEN                             | V1(5:0)  |             |          |  |

| 0x41     |                       |             | CSTAF   | RT1(5:0)          |                                  |          | CPOL        | Y1(1:0)  |  |

| 0x42     | 0                     | ENDC2       |         |                   | DLEN                             | 12(5:0)  |             |          |  |

| 0x43     |                       |             | CSTAF   | RT2(5:0)          |                                  |          | CPOL        | .Y2(1:0) |  |

| 0x44     |                       |             |         | BUS               | Y(7:0)                           |          |             |          |  |

| 0x45     | RSSI                  | ENSSI       | CMD2EN  | CMD01DI           | ASID                             | TOS      | NTOA        | REGPROT  |  |

| OPERAT   | TON                   |             |         |                   |                                  |          |             |          |  |

| 0x46     | 0                     | 0           | 0       | 0                 | 0                                | USDST 1) | BANKSW      | ACQMODE  |  |

| FAST SE  | NSOR INTER            | FACE: SPI M | ASTER   |                   |                                  |          |             |          |  |

| 0x47     | OSCDIV2 <sup>2)</sup> | ENFSI       |         |                   | DLFSI(5:0)                       |          |             |          |  |

| 0x48     | 0                     | IDLE        | STAF    | SI(1:0)           |                                  | HEAD     | DL(3:0)     |          |  |

| 0x49     |                       | CLKD        | IV(3:0) |                   | G2B                              | REQ_FT   | СРНА        | CPOL     |  |

| 0x4A     |                       |             |         | HEADI             | ER(7:0)                          |          |             |          |  |

| RESERV   | 'ED                   |             |         |                   |                                  |          |             |          |  |

| 0x4B     | 0                     | 0           | 0       | 0                 | 0                                | 0        | 0           | 0        |  |

| I/O CRO  | SSBAR                 |             |         |                   |                                  |          |             |          |  |

| 0x4C     | CB_SLO                | CB_SLI      | CB_MAO  | CB_IRQ            | CB_CLK                           |          | CB_FSI(2:0) |          |  |

| STARTU   | Р                     |             |         |                   |                                  |          |             |          |  |

| 0x4D     | CFGOK                 | 0           | ESE     | 0                 |                                  | CHPR     | EL(3:0)     |          |  |

| BiSS CC  | NTROL COM             | MUNICATION  |         |                   |                                  |          |             |          |  |

| 0x4E     |                       |             |         | RDATA(7:0)        |                                  |          |             |          |  |

| 0x4F     | 0                     | 0           | 0       | CONFIRM 1)        | IVALID <sup>1)</sup> CVALID(2:0) |          |             |          |  |

| Notes    |                       |             |         |                   |                                  |          |             |          |  |

|          |                       | •           |         | f not implemented |                                  |          |             |          |  |

Table 2: Configuration RAM (Access via SPI)

## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 12/36

## **REGISTER MAP (BISS)**

| ۸ddr     | Dit 7                 | Bit 6       | Bit 5    | Bit 4      | Bit 3       | Bit 2    | Bit 1       | Bit 0   |

|----------|-----------------------|-------------|----------|------------|-------------|----------|-------------|---------|

| Addr     | Bit 7                 |             | Bit 5    | Bit 4      | Bit 3       | BILZ     | BILI        | Bit 0   |

| FIELD II | NTERFACE: B           | iSS/SSI     |          |            |             |          |             |         |

| 0x60     | GRAY1                 | ENDC1       |          |            | DLEN        | N1(5:0)  |             |         |

| 0x61     |                       |             | CSTAF    | RT1(5:0)   |             |          | CPOL        | Y1(1:0) |

| 0x62     | 0                     | ENDC2       |          |            | DLEN        | N2(5:0)  |             |         |

| 0x63     |                       |             | CSTAF    | RT2(5:0)   |             |          | CPOL        | Y2(1:0) |

| 0x64     |                       |             |          | BUS        | Y(7:0)      |          |             |         |

| 0x65     | RSSI                  | ENSSI       | CMD2EN   | CMD01DI    | ASID        | TOS      | NTOA        | REGPROT |

| OPERA    | TION                  |             |          |            |             |          |             |         |

| 0x66     | 0                     | 0           | 0        | 0          | 0           | USDST 1) | BANKSW      | ACQMODE |

| FAST S   | ENSOR INTER           | FACE: SPI N | IASTER   |            |             |          | 1           | ·       |

| 0x67     | OSCDIV2 <sup>2)</sup> | ENFSI       |          |            | DLFS        | SI(5:0)  |             |         |

| 0x68     | 0                     | IDLE        | STAF     | SI(1:0)    |             | HEAD     | DL(3:0)     |         |

| 0x69     |                       | CLKE        | OIV(3:0) |            | G2B         | REQ_FT   | СРНА        | CPOL    |

| 0x6A     |                       |             |          | HEADE      | ER(7:0)     |          | •           |         |

| RESER    | /ED                   |             |          |            |             |          |             |         |

| 0x6B     | 0                     | 0           | 0        | 0          | 0           | 0        | 0           | 0       |

| I/O CRC  | SSBAR                 |             | '        |            | '           |          |             |         |

| 0x6C     | CB_SLO                | CB_SLI      | CB_MAO   | CB_IRQ     | CB_CLK      |          | CB_FSI(2:0) |         |

| STARTU   | JP                    |             | 1        | •          |             | '        |             |         |

| 0x6D     | CFGOK                 | 0           | ESE      | 0          | CHPREL(3:0) |          |             |         |

| BiSS C   | ONTROL COM            | MUNICATION  | 1        | •          | •           |          |             |         |

| 0x6E     |                       |             |          | RDAT       | A(7:0)      |          |             |         |

| 0x6F     | 0                     | 0           | 0        | CONFIRM 1) | IVALID 1)   |          | CVALID(2:0) |         |

| Notes    |                       |             | <u>'</u> | <u> </u>   |             | <u> </u> |             |         |

Other registers can only be accessed via BiSS, if implemented by the Host MCU as described in chapter BiSS Control Communication.

Table 3: Configuration RAM (Access via BiSS)

$<sup>^{1)}</sup>$  Not implemented before chip revision Z. Must be zero if not implemented.

$<sup>^{2)}</sup>$  Not implemented from chip revision Z. Must be zero if not implemented.

### SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 13/36

#### STARTUP AND OPERATION

#### Startup

After power on the configuration RAM is automatically initialized with zeros and must then be programmed through the host (SPI) or the field (BiSS) interface. If the host (SPI) interface is used, it is recommended to set REGPROT to avoid access to iC-MCB's configuration via BiSS.

Depending on USDST, the Data RAM needs to be initialized with valid data by the host MCU (SPI).

The chip release can be verified with the ROM value CHPREL.

| CHPREL     | Addr. 0x4D (SPI);  | bit 3:0 | R |

|------------|--------------------|---------|---|

|            | Addr. 0x6D (BiSS); | bit 3:0 | R |

| 0x0        | iC-MCB             |         |   |

| 0x1        | Reserved           |         |   |

| 0x2        | iC-MCB 2           |         |   |

| 0x3        | iC-MCB 3           |         |   |

| 0x4        | iC-MCB Z           |         |   |

| 0x5<br>0xF | Reserved           |         |   |

Table 4: Chip release

After the configuration phase, which will end by setting the parameter CFGOK, the device is ready for BiSS respectively SSI access. While CFGOK is zero, the data output SLO remains high to allow error detection in the SSI output format; the device listens to a write access via BiSS.

| CFGOK | Addr. 0x4D (SPI);             | bit 7      | R/W 0   |

|-------|-------------------------------|------------|---------|

|       | Addr. 0x6D (BiSS);            | bit 7      | R/W 0   |

| 0     | Configuration data invalid, S | SLO remair | ns high |

| 1     | Configuration data valid      |            |         |

Table 5: Tag configuration data as valid

### Operation

The iC-MCB provides sensor data after receiving the request from the BiSS Interface. Therefore, two interfaces are implemented to import sensor data to the Data RAM.

SPI master: The iC-MCB is active and uses a SPI master as a Fast Sensor Interface (FSI) to load sensor data from an external serial sensor. The interface is enabled with ENFSI. Detailed information can be found in chapter FAST SENSOR INTERFACE: SPI MASTER on page 29. SPI slave: The iC-MCB is passive and receives sensor data from a microprocessor using the host interface. Further details are described in chapter HOST INTERFACE: SPI SLAVE on page 19.

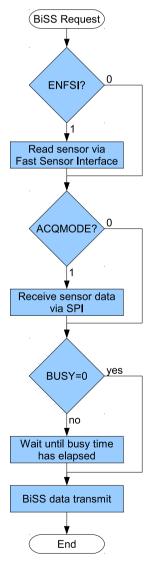

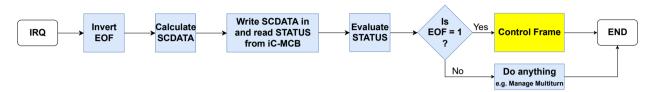

The operating sequence is shown in Figure 4. After a BiSS request the sensor data must be placed in the Data RAM. The following data transmission starts after a configurable delay to allow subsequent BiSS slaves to calculate their sensor data (see parameter BUSY). Unlike to the loading of sensor data via the Fast Sensor Interface, which starts always isochronic to the BiSS request, the microprocessors has two acquisition options.

Figure 4: Sequence diagram

If ACQMODE = 1, the iC-MCB waits after signalizing the request with IRQ until sensor data is written with a particular SPI command (Transmit SDAD) into the 64

## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 14/36

byte Data RAM. In the meantime the incomming data at SLI will be stored in the Data RAM. The host must finish operation Transmit SDAD before the temporary buffer overflows to prevent data loss.

If ACQMODE = 0, the iC-MCB does not wait for Transmit SDAD. Instead sensor data are either written into the Data RAM independently and asynchronously to the BiSS/SSI frames via the host interface or automatically requested by iC-MCB's Fast Sensor Interface. In the first case the last stored sensor data is transmitted in the next BiSS/SSI frame without any additional delay. In the latter case iC-MCB delays the start bit of the BiSS frame until the sensor data has been completely received via the Fast Sensor Interface.

| ACQMODE | Addr. 0x46 (SPI);                          | bit 0      | R/W 0 |

|---------|--------------------------------------------|------------|-------|

|         | Addr. 0x66 (BiSS);                         | bit 0      | R/W 0 |

| 0       | Independent of Transmit SDAD (SSI or BiSS) |            |       |

| 1       | Waiting for Transmit SDAD                  | (BiSS only | )     |

| Notes   | See Table 10 for application               | n details. |       |

Table 6: Acquisition mode

If sensor data is provided via the host interface and AC-QMODE = 0, it is necessary to enable bank switching with parameter BANKSW, which separates the Data RAM into three banks and a temporary buffer with 16 bytes each.

| BANKSW | Addr. 0x46 (SPI);                              | bit 1      | R/W 0 |

|--------|------------------------------------------------|------------|-------|

|        | Addr. 0x66 (BiSS);                             | bit 1      | R/W 0 |

| 0      | Bank switch disabled (one bank, see Table 35)  |            |       |

| 1      | Bank switch enabled (three banks, see Table 9) |            |       |

| Notes  | See Table 10 for application                   | n details. |       |

Table 7: Bank switch

Three banks are written alternately by the microcontroller (iC-MCB manages the bank selection automatically) and the fourth bank is used to temporarily store the last sent data. If no new sensor data has been written to iC-MCB by the microcontroller since the last BiSS frame, the parameter USDST configures, if the last sent sensor data is repeated (available in BiSS and mandatory in SSI), or if the sensor data is marked as invalid by sending zero data (available only in BiSS). In order to output proper data when using USDST = 1, the Data RAM needs to be initialized after power-on.

| USDST | Addr. 0x46 (SPI);                                         | bit 2        | R/W 0           |

|-------|-----------------------------------------------------------|--------------|-----------------|

|       | Addr. 0x66 (BiSS);                                        | bit 2        | R/W 0           |

| 0     | Send zero data (BiSS only)                                | )            |                 |

| 1     | Use sensor data several tin                               | nes (manda   | ntory in SSI)   |

| Notes | 1) USDST is not implemente                                | ed before cl | nip revision Z. |

|       | 2) See Table 10 for applicat                              | ion details. |                 |

|       | 3) If USDST = 1, the Data RA with proper data before sett |              |                 |

Table 8: Activity on missing sensor data

**Note:** The activity on missing sensordata is not defined before chip revision Z.

Table 9 shows the arrangement in the Data RAM if BANKSW is set.

| Data RAM     | Addr. 0x000x3F (SPI); bit 7:0 R/W 0        |

|--------------|--------------------------------------------|

| 0x00<br>0x0F | Bank 0                                     |

| 0x10<br>0x1F | Bank 1                                     |

| 0x20<br>0x2F | Bank 2                                     |

| 0x30<br>0x3F | Temporary buffer for data received at SLI. |

Table 9: Data RAM arrangement (BANKSW=1)

|                 | Application    |                             | Start Bit Delay at            | Recommer |        |        |

|-----------------|----------------|-----------------------------|-------------------------------|----------|--------|--------|

| Field Interface | Sensor Data    | SPI Operation <sup>1)</sup> | Field Interface <sup>2)</sup> | ACQMODE  | BANKSW | USDST  |

| BiSS (ENSSI=0)  | Input via Host | Synchronous                 | Waiting for Transmit SDAD     | 1        | 0      | 0      |

| SSI (ENSSI=1)   | Input via Host | Asynchronous                | No delay                      | 0        | 1      | 1      |

| BiSS (ENSSI=0)  | Input via FSI  | Synchronous                 | Waiting for FSI               | 0        | 0      | 0      |

| BiSS (ENSSI=0)  | Input via Host | Asynchronous                | No delay                      | 0        | 1      | 0 or 1 |

#### Notes:

<sup>1)</sup> Synchronous operation at the host interface is enabled with IRQ.

<sup>&</sup>lt;sup>2)</sup> Only in BiSS a sensor's processing time can be considered. iC-MCB delays the start bit of the BiSS frame while waiting for sensor data (until the rising edge of signal NCS at host interface or FSI respectively). The minimum start bit delay (BUSY) is considered and the start bit is additionally delayed as defined in 1002 and 1003.

### SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 15/36

#### **FIELD INTERFACE: General**

iC-MCB provides one RS422 line receiver for the clock input MA and one current limited RS422 driver for the data output SLO. The line receiver includes internal resistors to allow a common mode voltage range of -7 V to +7 V. A single ended TTL mode for MA can be selected with the parameter ESE.

| ESE | Addr. 0x4D (SPI);            | bit 5     | R/W 0 |

|-----|------------------------------|-----------|-------|

|     | Addr. 0x6D (BiSS);           | bit 5     | R/W 0 |

| 0   | Differential ended operation | at MA, NI | MA    |

| 1   | Single-ended operation at N  | 1A        |       |

Table 11: Enable single ended operation

#### FIELD INTERFACE: BISS

The BiSS Interface is a serial, bidirectional interface which is suitable to transmit process data isochronously and to access memory registers (e.g. an electronic

datasheet) of the slave device. For a detailed description of the protocol refer to the BiSS C Protocol Description.

#### **BiSS Frame**

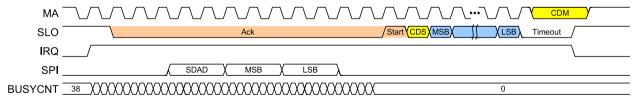

A BiSS frame is used to interchange process data between master and slave and to transmit one bit in each direction for the control communication. Process data is distinguished into sensor data, which is transferred from slave to master, and actuator data for the opposite direction. The iC-MCB signalizes the start of each frame with IRQ at the first rising edge of MA. This first rising edge signals the slave to capture its sensor data and is in BiSS defined as the 'latch point'. Now the iC-MCB waits for sensor data (ACQMODE = 1), which must be provided via SPI with the command Transmit SDAD. The start bit is then generated when both the SPI command Transmit SDAD has been completed and the busy counter (configured by BUSY and measured from the latch point) has expired.

| BUSY | Addr.       | 0x44 (SPI);  | bit 7:0       | R/W 0     |

|------|-------------|--------------|---------------|-----------|

|      | Addr.       | 0x64 (BiSS); | bit 7:0       | R/W 0     |

| Code |             | Minimum st   | art bit delay |           |

|      | before chip | release Z    | from chip     | release Z |

|      | In clocks   | Time         | In clocks     | Time      |

|      | fosc        | period       | fosc          | period    |

| 0x00 | 0           | 0 ns         | 0             | 0 ns      |

| 0x01 | 1           | 50 ns        | 4             | 200 ns    |

| 0x02 | 2           | 100 ns       | 8             | 400 ns    |

| 0xFE | 254         | 12.7 µs      | 1016          | 50.8 µs   |

| 0xFF | 255         | 12.75 µs     | 1020          | 51 µs     |

Table 12: Minimum start bit delay

Figure 5: Start bit delay in BiSS frame

The process data is contained in logical data channels. Each data channel has a programmable data length (DLEN1, DLEN2) and CRC to increase the transmission safety. The generator polynomial (CPOLY1, CPOLY2) and the start value for CRC calculation (CSTART1, CSTART2) is programmable too. ENDC1 and ENDC2 enable the corresponding data channel. With the BiSS protocol two channels can be configured in iC-MCB. Process data contained in data channel 1 is received by the BiSS master first, followed by the process data in data channel 2.

| DLEN1 | Addr. 0x40 (SPI);          | bit 5:0      | R/W 0       |

|-------|----------------------------|--------------|-------------|

|       | Addr. 0x60 (BiSS);         | bit 5:0      | R/W 0       |

| 0x00  | 1 bit                      |              |             |

|       | (DLEN1 + 1) bit            |              |             |

| 0x3F  | 64 bit                     |              |             |

| Notes | If DLEN1 < 8, a CRC must b | e enabled (C | POLY1 > 0). |

Table 13: Data length channel 1

## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 16/36

| ENDC1 | Addr. 0x40 (SPI);       | bit 6 | R/W 0 |

|-------|-------------------------|-------|-------|

|       | Addr. 0x60 (BiSS);      | bit 6 | R/W 0 |

| 0     | Data channel 1 disabled |       |       |

| 1     | Data channel 1 enabled  |       |       |

Table 14: Enable data channel 1

| CPOLY1 | Addr. 0x41 (SPI);          | bit 1:0     | R/W 0      |

|--------|----------------------------|-------------|------------|

|        | Addr. 0x61 (BiSS);         | bit 1:0     | R/W 0      |

| 0x0    | no CRC generated (0 bit CF |             |            |

| 0x1    | CRC polynomial = 0x25 (5 l | bit CRC)    |            |

| 0x2    | CRC polynomial = 0x43 (6 l |             |            |

| 0x3    | CRC polynomial = 0x190D9   | (16 bit CRC | <b>;</b> ) |

Table 15: CRC polynomial data channel 1

| CSTART1      | Addr. 0x41 (SPI);             | bit 7:2 | R/W 0 |

|--------------|-------------------------------|---------|-------|

|              | Addr. 0x61 (BiSS);            | bit 7:2 | R/W 0 |

| 0x00<br>0x3F | Start value for CRC calculate | tion    |       |

Table 16: CRC start value for data channel 1

| DLEN2 | Addr. 0x42 (SPI);                                 | bit 5:0 | R/W 0 |

|-------|---------------------------------------------------|---------|-------|

|       | Addr. 0x62 (BiSS);                                | bit 5:0 | R/W 0 |

| 0x00  | 1 bit                                             |         |       |

| •••   | (DLEN2 + 1) bit                                   |         |       |

| 0x3F  | 64 bit                                            |         |       |

| Notes | If DLEN2 < 8, a CRC must be enabled (CPOLY2 > 0). |         |       |

Table 17: Data length channel 2

| ENDC2 | Addr. 0x42 (SPI);                             | bit 6      | R/W 0          |

|-------|-----------------------------------------------|------------|----------------|

|       | Addr. 0x62 (BiSS);                            | bit 6      | R/W 0          |

| 0     | Data channel 2 disabled: da                   | ata channe | l length 0 bit |

| 1     | Data channel 2 enabled (condition: ENDC1 = 1) |            |                |

Table 18: Enable data channel 2

| CPOLY2 | Addr. 0x43 (SPI);                      | bit 1:0 | R/W 0 |

|--------|----------------------------------------|---------|-------|

|        | Addr. 0x63 (BiSS);                     | bit 1:0 | R/W 0 |

| 0x0    | no CRC2 generated (0 bit CRC)          |         |       |

| 0x1    | CRC2 polynomial = 0x25 (5 bit CRC)     |         |       |

| 0x2    | CRC2 polynomial = 0x43 (6 bit CRC)     |         |       |

| 0x3    | CRC2 polynomial = 0x190D9 (16 bit CRC) |         |       |

Table 19: CRC polynomial data channel 2

| CSTART2      | Addr. 0x43 (SPI);           | bit 7:2 | R/W 0 |

|--------------|-----------------------------|---------|-------|

|              | Addr. 0x63 (BiSS);          | bit 7:2 | R/W 0 |

| 0x00<br>0x3F | Start value for CRC calcula | tion    |       |

Table 20: CRC start value for data channel 2

The (automatic) BiSS timeout adaption (refer to www.biss-interface.com) is based on the BiSS MA clock period  $T_{MA}$  and the device specific internal sampling frequency  $1/T_{CLK}$ .

The iC-MCB measures the 1.5 periods (from the first falling to the second rising edge) of MA each frame and calculates an adaptive timeout with  $T_{CLK} = \frac{1.33}{f_{OSC}}$  (see El. Char. 225).

| Symbol  | Condition                                             | Min.                   | Max.                    |

|---------|-------------------------------------------------------|------------------------|-------------------------|

| timeout | $T_{CLK} \le 1.5 * T_{MA}$ $T_{CLK} \ge 1.5 * T_{MA}$ | 1.5 * T <sub>MA</sub>  | 1.5 * T <sub>MA</sub> + |

|         |                                                       |                        | 3.0 * T <sub>CLK</sub>  |

|         | $T_{CLK} \geq 1.5*T_{MA}$                             | 1.0 * T <sub>CLK</sub> | 1.5 * T <sub>MA</sub> + |

|         |                                                       |                        | 3.0 * T <sub>CLK</sub>  |

Table 21: Adaptive BiSS timeout

Parameters NTOA and TOS (described in chapter FIELD INTERFACE: SSI) may be considered to enable a constant long BiSS timeout (approx. 20 µs) or constant short BiSS timeout (approx. 2 µs) as well.

## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 17/36

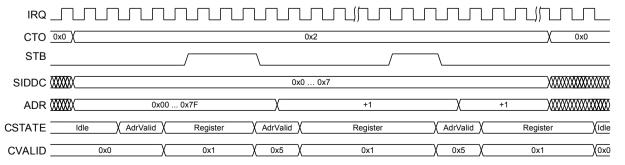

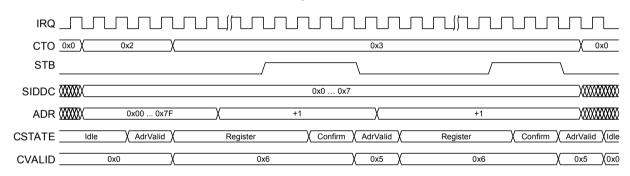

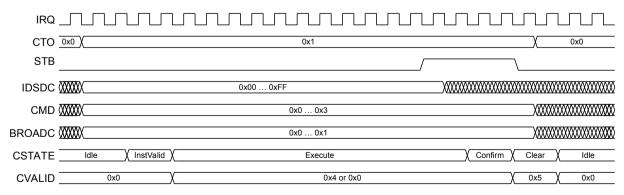

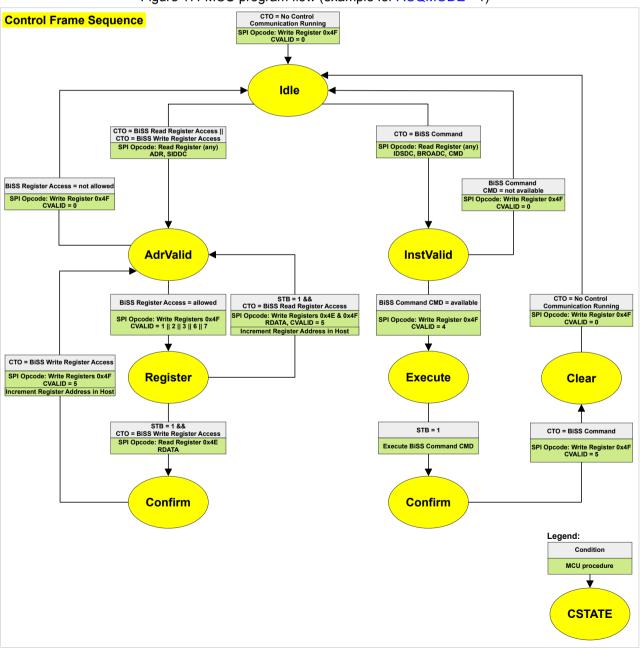

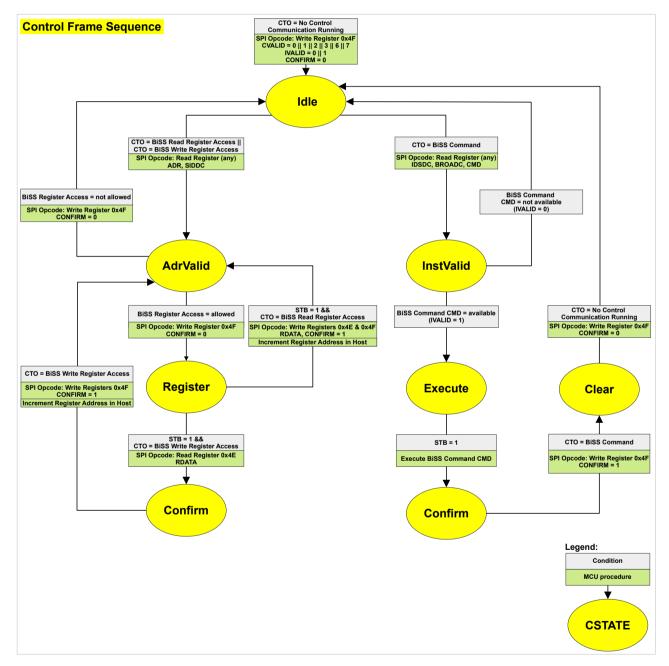

#### **BiSS Control Data Frame**

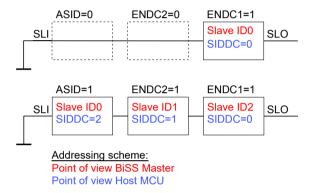

The iC-MCB manages a dedicated set of BiSS commands and registers automatically. The number of occupied slave IDs is equal to the number of enabled data channels, but can be increased by one using ASID.

If CFGOK is not set or if the SSI protocol is enabled, the control frame will be executed without evaluating the slave ID. A register overview is shown in Table 22.

| Addr. <sup>2)</sup> | Name                                  | Size              | Managed by |

|---------------------|---------------------------------------|-------------------|------------|

| 0x00 0x3F           | Register bank                         | 64 bytes          | Host       |

| 0x40                | Bank selection                        | 08 bits (1 byte)  | Host       |

| 0x41                | EDS bank                              | 08 bits (1 byte)  | Host       |

| 0x42 0x43           | Profile ID                            | 16 bits (2 bytes) | Host       |

| 0x44 0x47           | Serial number                         | 32 bits (4 bytes) | Host       |

| 0x48 0x5F           | Slave register                        | 24 bytes          | Host       |

| 0x60 0x6F 1)        | Config RAM                            | 16 bytes          | iC-MCB     |

| 0x70 0x77           | Slave register                        | 8 bytes           | Host       |

| 0x78 0x7D           | Device ID                             | 48 bits (6 bytes) | Host       |

| 0x7E 0x7F           | Manufacturer ID                       | 16 bits (2 bytes) | Host       |

|                     | · · · · · · · · · · · · · · · · · · · | ·                 |            |

#### Notes:

Table 22: BiSS Register Assignment

| ASID | Addr. 0x45 (SPI);                                                                                                                                                                                                          | bit 3    | R/W 0  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|

|      | Addr. 0x65 (BiSS);                                                                                                                                                                                                         | bit 3    | R/W 0  |

| 0    | Additional slave ID deactivate occupied slave IDs is  • 0, if ENDC1 = 0, ENDC2 = 0  • 1, if ENDC1 = 1, ENDC2 = 0  • 2, if ENDC1 = 1, ENDC2 = 0                                                                             | ))<br>)) | per of |

| 1    | <ul> <li>2, if ENDC1=1, ENDC2=1)</li> <li>Additional slave ID activated. The number of occupied slave IDs is</li> <li>1, if ENDC1=0, ENDC2=0)</li> <li>2, if ENDC1=1, ENDC2=0)</li> <li>3, if ENDC1=1, ENDC2=1)</li> </ul> |          |        |

Table 23: Activate additional Slave ID

The BiSS commands with the codes 0 and 1 are managed by iC-MCB, but they can be disabled per configuration bit CMD01DI.

| CMD01DI | Addr. 0x45 (SPI);<br>Addr. 0x65 (BiSS); | bit 4<br>bit 4 | R/W 0<br>R/W 0 |

|---------|-----------------------------------------|----------------|----------------|

| 0       | Enable BiSS commands 0                  | and 1          |                |

| 1       | Disable BiSS commands 0 and 1           |                |                |

Table 24: BiSS Command 0/1 Control

Parameter CMD2EN configures if the BiSS command with opcode 2 is managed by iC-MCB or by the host. In iC-MCB the command opcode 2 is used to switch the signal level at I/O crossbar pin BK, e.g. to control a bus

coupler. CMD2EN enables pin BK at the I/O crossbar with respect to the priority shown in Table 67.

| CMD2EN | Addr. 0x45 (SPI);                          | bit 5 | R/W 0 |

|--------|--------------------------------------------|-------|-------|

|        | Addr. 0x65 (BiSS);                         | bit 5 | R/W 0 |

| 0      | BiSS command 2 managed by host             |       |       |

| 1      | BiSS command 2 enabled (control BK at IOx) |       |       |

Table 25: BiSS Command 2 Control

For access to iC-MCB's Config RAM via BiSS register addresses 0x60 to 0x6F are used. The access is denied, if REGPROT is set.

| REGPROT | Addr. 0x45 (SPI);                                                                             | bit 0 | R/W 0 |

|---------|-----------------------------------------------------------------------------------------------|-------|-------|

|         | Addr. 0x65 (BiSS);                                                                            | bit 0 | R/W 0 |

| 0       | BiSS access to iC-MCB's Config RAM allowed                                                    |       |       |

| 1       | BiSS access to iC-MCB's Config RAM denied                                                     |       |       |

| Notes   | It is recommended to set REGPROT = 1 before setting CFGOK = 1, if the host interface is used. |       |       |

Table 26: Register protection

All BiSS commands and register accesses that are not managed by iC-MCB have to be managed by the host as described in chapter BiSS Control Communication on page chapter 22ff.

<sup>&</sup>lt;sup>1)</sup> Access to the Config RAM via BiSS is completely managed by iC-MCB. All other registers can only be accessed via BiSS, if implemented by the Host MCU as described in chapter BiSS Control Communication.

<sup>2)</sup> Further hints and requirements for BiSS C slave register implementations are available in the BiSS C Protocol Description.

### SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 18/36

#### FIELD INTERFACE: SSI

Note the hints in chapter DESIGN REVIEW: Notes On Chip Functions.

The interface uses the SSI protocol when ENSSI is set.

| ENSSI | Addr. 0x45 (SPI);                         | bit 6 | R/W 0 |

|-------|-------------------------------------------|-------|-------|

|       | Addr. 0x65 (BiSS);                        | bit 6 | R/W 0 |

| 0     | BiSS C protocol                           |       |       |

| 1     | SSI protocol                              |       |       |

| Notes | For operation in SSI mode, set USDST = 1. |       |       |

Table 27: Protocol selection

#### The SSI frame

The SSI frame is used to transmit process data from a sensor to a master. The process data is contained

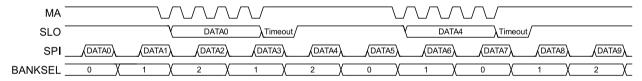

in logical data channels. Each data channel has a programmable data length (DLEN1, DLEN2) and CRC to increase the transmission safety. The generator polynomial (CPOLY1, CPOLY2) and the start value for CRC calculation (CSTART1, CSTART2) is programmable too. ENDC1 and ENDC2 enable the corresponding data channel. As the SSI protocol does not support the delayed transmission of sensor data, the data must already be stored in the RAM when the SSI frame starts (ACQMODE = 0, BANKSW = 1, USDST = 1). The banks are automatically switched after writing into the data RAM with the SPI command Transmit SDAD. Fig. 6 shows the active RAM bank with BANKSEL indicating the currently selected bank.

Figure 6: SSI frame

### Serial timeout

For SSI operation the adaptive timeout is not recommended. A fixed timeout is enabled with NTOA with a length selected by TOS.

| NTOA | Addr. 0x45 (SPI);                                    | bit 1 | R/W 0 |

|------|------------------------------------------------------|-------|-------|

|      | Addr. 0x65 (BiSS);                                   | bit 1 | R/W 0 |

| 0    | Adaptive timeout enabled (TOS configuration not rele | vant) |       |

| 1    | Adaptive timeout disabled (TOS configuration relevan | t)    |       |

Table 28: Adaptive timeout

| TOS | Addr. 0x45 (SPI);            | bit 2 | R/W 0 |

|-----|------------------------------|-------|-------|

|     | Addr. 0x65 (BiSS);           | bit 2 | R/W 0 |

| 0   | Long timeout (approx. 20 µs  | s)    |       |

| 1   | Short timeout (approx. 2 µs) | )     |       |

Table 29: Serial timeout

$egin{bmatrix} \mathbf{i} \end{bmatrix}$

The fixed short or long timeout can also be used with the BiSS protocol.

#### **Data format**

A binary-to-Gray conversion can be enabled with GRAY1. With the SSI protocol two channels can be

configured in iC-MCB to separate Gray-coded content in data channel 1 and following non-Gray-coded content in data channel 2. If the data contains additional SSI data bits which shall not be converted to Gray-code, those additional bits can be placed in data channel 2.

| GRAY1 | Addr. 0x40 (SPI);         | bit 7 | R/W 0 |

|-------|---------------------------|-------|-------|

|       | Addr. 0x60 (BiSS);        | bit 7 | R/W 0 |

| 0     | No data conversion        |       |       |

| 1     | Binary-to-Gray conversion |       |       |

Table 30: SSI data format

#### Ring operation

The ring operation, which is selected with RSSI, defines a ring buffer with the data channel 1. In ring operation the data channel 2 can be used to define one or more bits, e.g. one stop bit, to separate the repetition.

| RSSI  | Addr. 0x45 (SPI);                                                              | bit 7    | R/W 0   |

|-------|--------------------------------------------------------------------------------|----------|---------|

|       | Addr. 0x65 (BiSS);                                                             | bit 7    | R/W 0   |

| 0     | Ring operation disabled                                                        |          |         |

| 1     | Ring operation enabled                                                         |          |         |

| Notes | For ring operation at least t need to be used (DLEN1 ≥ ENDC2 = 1 or DLEN1 ≥ 16 | 8, ENDC1 | = 1 and |

Table 31: Ring operation

## SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 19/36

### **HOST INTERFACE: SPI SLAVE**

### **SPI Signals**

| Signal           | Description                               |  |  |  |

|------------------|-------------------------------------------|--|--|--|

| SPI Sla          | ve Signals                                |  |  |  |

| NCS              | Not chip select Input                     |  |  |  |

| SCLK             | SPI clock Input                           |  |  |  |

| MOSI             | SPI data Input                            |  |  |  |

| MISO             | SPI data Output, if NCS = 0               |  |  |  |

|                  | High impedance, if NCS = 1                |  |  |  |

| Optional Signals |                                           |  |  |  |

| IRQ              | Interrupt Output (if enabled with CB_IRQ) |  |  |  |

Table 32: SPI Slave Signals

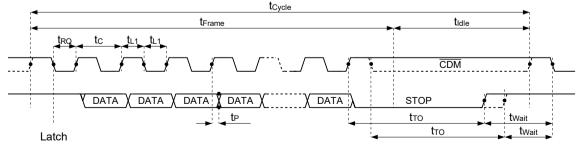

#### **SPI Frame**

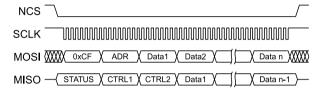

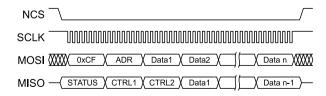

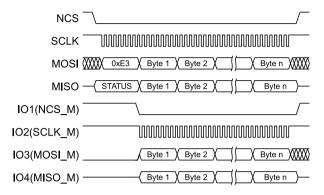

Each SPI frame starts with one byte OPCODE sent from the host via MOSI and one byte STATUS sent from iC-MCB via MISO.

Figure 7: SPI frame example with OPCODE(0xCF), STATUS, CTRL1 and CTRL2

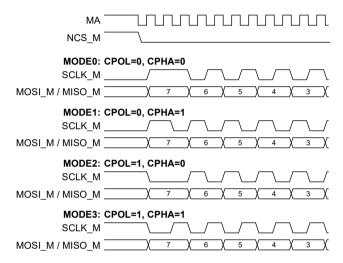

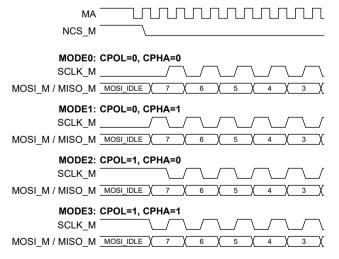

#### **SPI Modes**

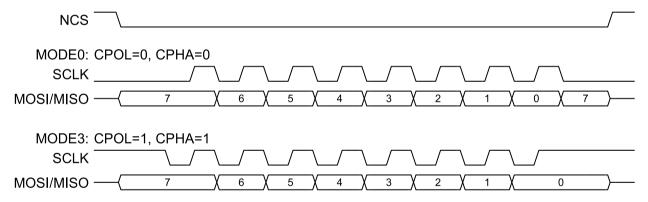

The iC-MCB uses 8 bit wide SPI with phase and polarity = 0, or phase and polarity = 1.

Figure 8: SPI: timing, phase and polarity

### **SPI Registers**

The host uses the SPI interface to configure iC-MCB at startup and to write sensor data to iC-MCB.

Table 33 shows the register assignment for the SPI access.

| Addr.     | Name       | Size     | Access Level |

|-----------|------------|----------|--------------|

| 0x00 0x3F | Data RAM   | 64 bytes | R/W          |

| 0x40 0x4F | Config RAM | 16 bytes | R/W          |

Table 33: Table of register assignment

### SPI-TO-BISS BRIDGE WITH RS422 TRANSCEIVER

Rev C1, Page 20/36

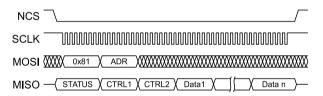

### **SPI Opcodes**

The following opcodes are available.

| OPCODE |                    |

|--------|--------------------|

| Code   | Description        |

| 0xA6   | Transmit SDAD      |

| 0x81   | Read Register      |

| 0xCF   | Write Register     |

| 0xE3   | Sensor Feedthrough |

Table 34: SPI Opcodes

All bytes after the first STATUS byte sent from iC-MCB via MISO depend on the SPI OPCODE and may contain additional BiSS Control Communication Data CTRL1 and CTRL2 or related device data.

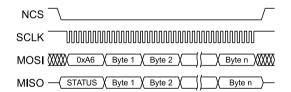

#### **SPI Opcode: Transmit SDAD**

To transmit sensor data to iC-MCB the SPI OPCODE 0xA6 is used. Following the opcode the Single-Cycle Data (SCDATA) is read from the Data RAM starting at address 0x00 as shown in 9.

Figure 9: SPI: sensor data access (SDAD)

Within the Data RAM the SCDATA is arranged big-endian, i.e. with the highest-value byte at the lowest-value address. The MSB of data channel 1 is at address 0x00 and the LSB is always at bit position zero. The data for channel 2 starts at the next higher address following the memory area of data channel 1. The maximum data length is 8 byte per channel. Table 35 shows an example of data arrangement with 14 bit SCDATA length for channel 1 and 27 bit SCDATA2 length for channel 2 in the Data RAM. An access to the Data RAM during the BiSS frame is permitted, if it is partitioned into multiple banks using BANKSW. Only as many bytes as configured with DLEN1 and DLEN2 may be input during SPI access.