Rev D5, Page 1/80

#### **FEATURES**

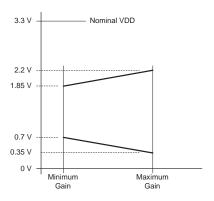

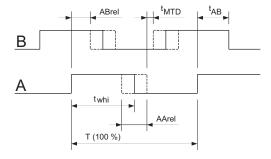

- ♦ Differential PGA inputs for sine, cosine, and index

- ♦ Input frequency of up to 700 kHz

- ♦ AB output frequency of up to 12.5 MHz

- ♦ Automatic compensation of amplitude, offset, and phase errors

- ♦ Low latency (typ. 1.5 µs)

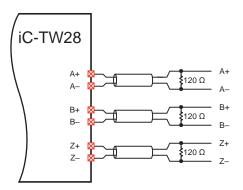

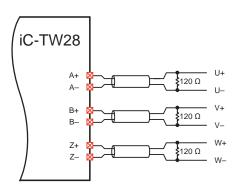

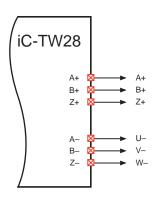

- ♦ Differential RS422 line driver outputs for ABZ or UVW

- ♦ Simultaneous single-ended outputs for ABZ and UVW

- ◆ Digital filtering for ultra-low output jitter

- ♦ Complete status and fault monitoring capabilities

- ♦ Configured by pins or SPI

- ♦ In-field re-configuration via Encoder Link interface

- ♦ Easy to use with built-in line driver, EEPROM, and oscillator

- ♦ Push-button automatic calibration for fast commissioning

- ♦ LED intensity control by PWM output

- ♦ 10-bit angle data and 14-bit multi-cycle counter available to SPI

- Capture register for coded reference marks and touch-probe applications

- ♦ Space-saving 5 x 5 mm QFN package

- ♦ Single 3.3 V supply

#### **APPLICATIONS**

- ♦ Rotary and linear encoders

- Magnetic or optical sin/cos sensor interface

- ♦ Brushless motor commutation (2...64 poles)

- ♦ Embedded motion control

#### **PACKAGES**

32-pin QFN 5 mm x 5 mm x 0.9 mm RoHS compliant

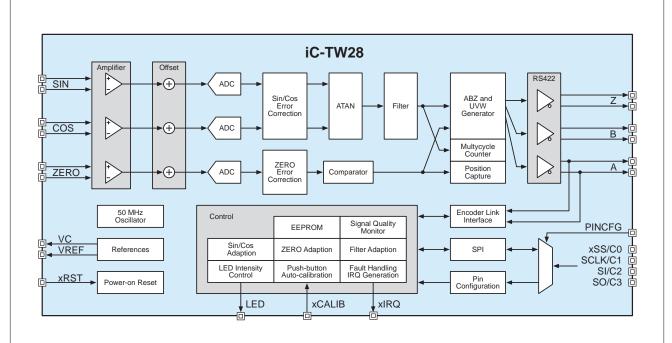

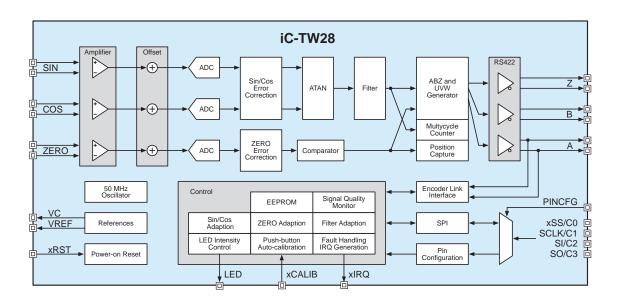

#### **BLOCK DIAGRAM**

Rev D5, Page 2/80

#### **DESCRIPTION**

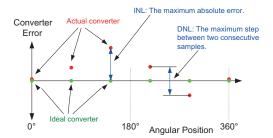

The iC-TW28 is a general purpose 10-bit application-specific interpolator for sine/cosine signals with automatic calibration and adaption of signal path parameters during operation to maintain minimum angular error and jitter. Angular position is calculated at a programmable resolution of up to 1024 increments per input cycle. Automatic calibration and adaption (correction during operation) of sensor offset, sin/cos amplitude match, and phase quadrature is provided. Additionally, automatic calibration of gain, offset and phase of the zero inputs allows for rapid commissioning.

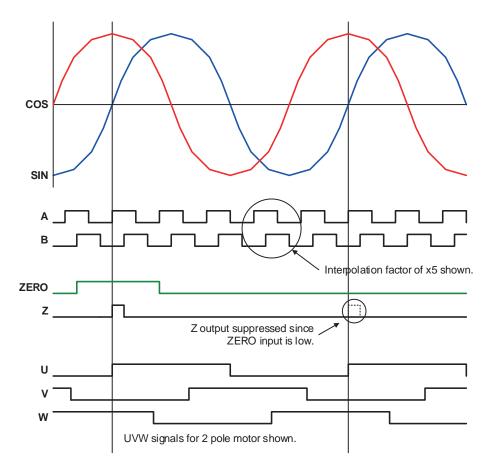

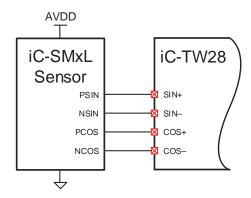

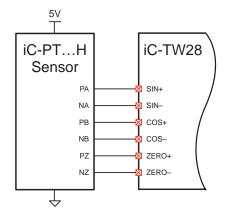

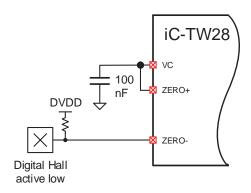

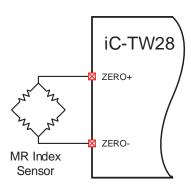

The iC-TW28 accepts 20 mV to 2 V differential Sin/Cos input signals directly from magnetic or optical sensors – no external signal conditioning is required in most applications. The differential zero input accepts a wide range of digital and analog index gating sources such as Hall or MR sensor bridges. The Z output width, position relative to the sin/cos inputs, and synchronization to the AB quadrature outputs is fully programmable.

In addition to industry-standard incremental ABZ quadrature output, the iC-TW28 provides optional UVW commutation output modes for 1 to 32 polepair motors and SPI angle and multi-cycle readout for embedded applications. The incremental ABZ quadrature output can be generated at a frequency of up to 12 MHz (20 ns edge spacing); the maximum output frequency can also be limited so as not to overwhelm connected counters or controllers.

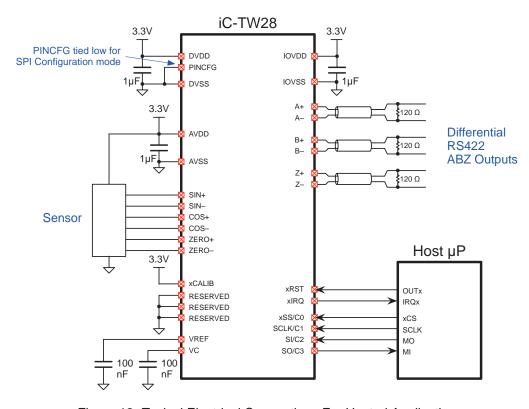

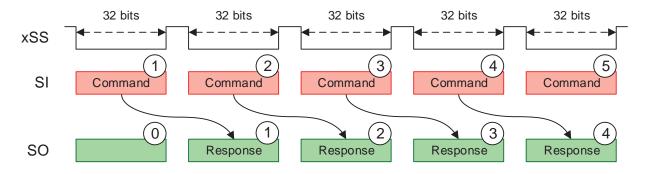

In SPI mode, the iC-TW28 provides multi-cycle synchronization and reference mark capture functions

to support absolute position systems. Higher input signal frequencies are allowed in SPI mode since the ABZ output frequency limitation is not applicable.

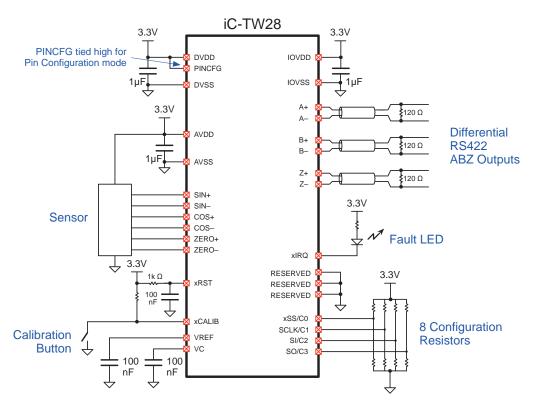

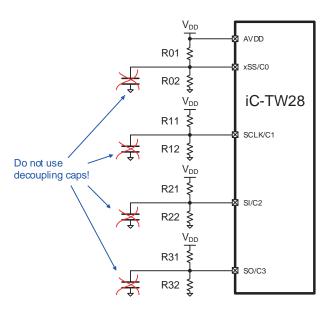

The iC-TW28 offers two configuration modes. Pin configuration mode provides simple, static configuration that does not require any programming or complicated calibration. Pin configuration mode uses a subset of the iC-TW28's complete capabilities including ABZ quadrature output, a limited choice of the most commonly used interpolation (resolution) and hysteresis values, and one-button calibration. Eight resistors set voltage levels at four configuration input pins to select all operating parameters, simplifying product assembly. One-button auto calibration sets input gain and compensates sensor offset and sin/cos channel gain match and phase with just a few input cycles and then stores the compensation values to the internal EEPROM.

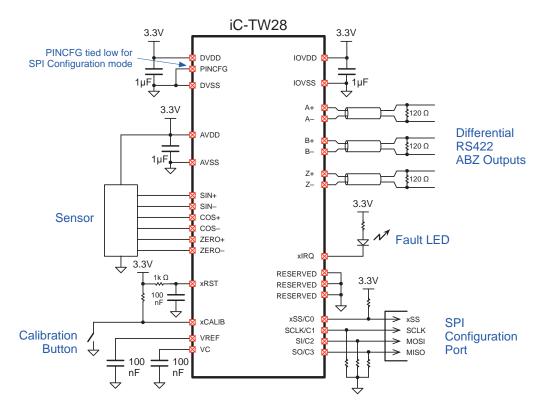

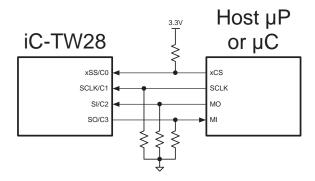

In more sophisticated applications, serial configuration mode allows access to all iC-TW28 features. Complete device configuration using the bi-directional SPI or Encoder Link ports provides access to all resolutions (including fractional interpolation), fully programmable hysteresis, and advanced noise/jitter filtering, quality monitoring, and fault detection capabilities.

The iC-TW28 requires no external components for operation. An EEPROM for storage of configuration and calibration data, and RS422 line drivers are already integrated on-chip. An integrated power-on reset circuit can be overridden by an external hardware reset signal if necessary.

Rev D5, Page 3/80

#### **CONTENTS**

| PACKAGING INFORMATION               | 5  | Residual Error Calculation (Serial Only) | 17       |

|-------------------------------------|----|------------------------------------------|----------|

| PIN CONFIGURATION QFN32-5x5         |    | EEPROM                                   | 17       |

| (top view)                          | 5  |                                          |          |

| PACKAGE DIMENSIONS                  | 6  | ELECTRICAL CONNECTIONS                   | 18       |

| PIN FUNCTIONS                       | 7  | Power and Ground                         | 20       |

| ABSOLUTE MAXIMUM RATINGS            | 0  | Reference Outputs                        | 20       |

| ABSOLUTE MAXIMUM RATINGS            | 8  | xCALIB Input                             | 20       |

| THERMAL DATA                        | 8  | SIN and COS Inputs                       | 21       |

|                                     |    | ZERO Inputs                              | 21       |

| ELECTRICAL CHARACTERISTICS          | 9  | ABZ Outputs                              | 21<br>22 |

| ODED ATIMO DEGLIDEMENTO             | 40 | UVW Outputs                              | 22       |

| OPERATING REQUIREMENTS              | 12 | xRST Input                               | 22       |

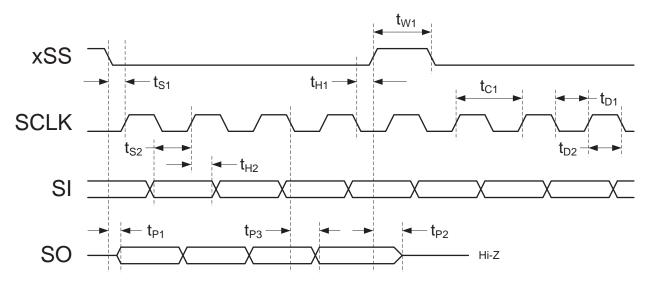

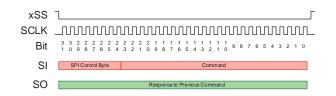

| SPI Interface                       | 12 | xIRQ Output                              | 22       |

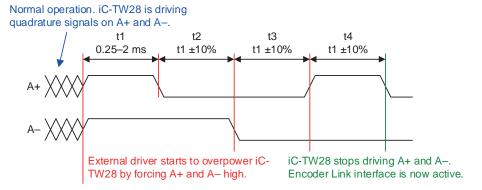

| Encoder Link Interface              | 13 | LED Output                               | 22       |

| FUNCTIONAL OVERVIEW                 | 14 | PINCFG Input                             | 23       |

|                                     | •  | SPI Port                                 | 23       |

| FUNCTIONAL BLOCK DIAGRAM            | 15 | Reserved Pins                            | 23       |

| Reference                           | 15 | Neserveu Filis                           | 23       |

| Oscillator                          | 15 | CONFIGURATION OVERVIEW                   | 24       |

| Power-On Reset                      | 15 | Pin Configuration Mode                   | 24       |

| SPI Port/Configuration Pins         | 15 | Interpolation Factor                     | 24       |

| Encoder Link Interface              | 15 | Hysteresis and Filtering                 | 24       |

| Input Stage                         | 15 | AB Frequency Limit and Auto Adaption     | 25       |

| Analog Error Correction             | 15 | Input Range, Interpolation Group, and Z  |          |

| Analog-to-Digital Converters (ADCs) | 15 | Calibration                              | 25       |

| Digital Error Correction            | 15 | Serial Configuration Mode                | 26       |

| Angle Calculation (Arctan)          | 16 | CALIBRATION OVERVIEW                     | 27       |

| Filter                              | 16 | Hardware Auto Calibration (xCALIB)       | 27       |

| Hysteresis                          | 16 | Software Auto Calibration                | 28       |

| Interpolation Factor                | 16 | Software Auto Cambration                 | 20       |

| Z Signal Path                       | 16 | STARTUP                                  | 28       |

| ABZ Generator                       | 16 |                                          |          |

| Post-AB Divider                     | 16 | SPI COMMUNICATION                        | 29       |

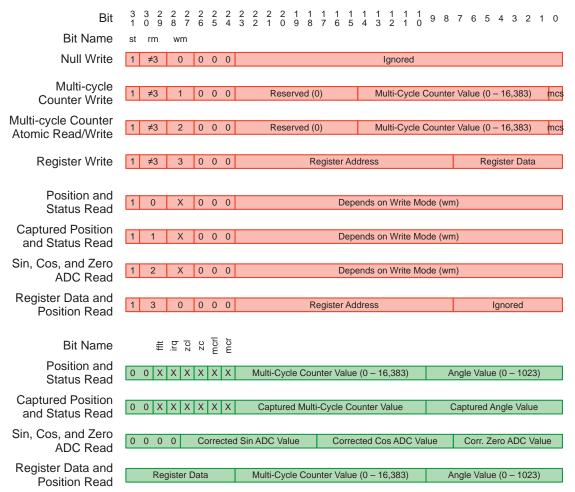

| UVW Signal Path                     | 16 | Command Packet Format                    | 30       |

| ABZ/UVW Outputs                     | 16 | Null Write (Read Only)                   | 31       |

| Auto Calibration                    | 16 | Multi-Cycle Counter Write                | 31       |

| Auto Adaption                       | 16 | Multi-Cycle Counter Atomic Read/Write    | 31       |

| Fault Handling                      | 16 | Register Write                           | 32       |

| AB Output Frequency Limiter         | 17 | Register Data and Position Read          | 32       |

| Amplitude Monitor                   | 17 | Response Packet Formats                  | 32       |

| LED Intensity Control (Serial Only) | 17 | Position and Status Read                 | 32       |

| Multi-Cycle Counter (Serial Only)   | 17 | Captured Position and Status Read        | 33       |

| Position Capture (Serial Only)      | 17 | Sin, Cos, and Zero ADC Read              | 33       |

| Filter Adaption (Serial Only)       | 17 | Register Data and Position Read          | 33       |

| Rev D5, Page 4/80 |

|-------------------|

|-------------------|

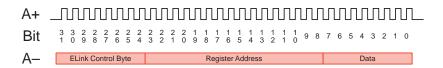

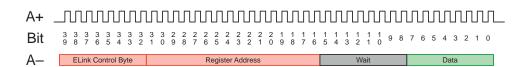

| ENCODER LINK COMMUNICATION | 34 | BASE Registers                        | 53  |

|----------------------------|----|---------------------------------------|-----|

| Encoder Link Write         | 35 | LIM Registers                         | 53  |

| Encoder Link Read          | 35 | RES Registers                         | 53  |

|                            |    | TH Registers                          | 54  |

| CONFIGURATION PARAMETERS   | 36 | WATCHDOG                              | 54  |

| Register Map               | 36 | SC_AMP                                | 54  |

| MAIN_CFG                   | 38 | S_AMP                                 | 54  |

| LED_CFG                    | 39 | C_AMP                                 | 54  |

| LED_START                  | 40 | DEVICE_ID                             | 54  |

| LED_PWM                    | 40 | REV0 and REV1                         | 54  |

| TEST                       | 40 |                                       |     |

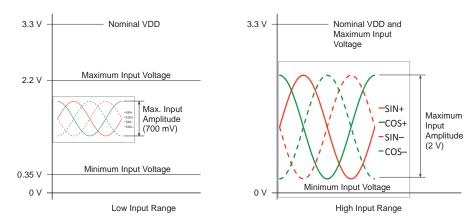

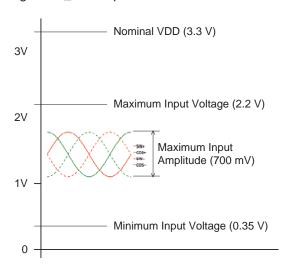

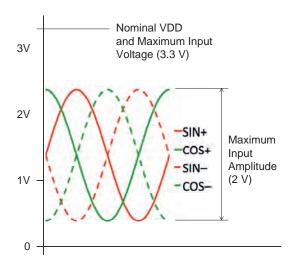

| UVW_CFG                    | 41 | INPUT CONFIGURATION AND SIGNAL LEVELS | 55  |

| INTER0                     | 41 | LEVELS                                | ວວ  |

| INTER1                     | 41 | OUTPUT MODES, DIRECTIONS, AND         |     |

| AB                         | 41 | POLARITIES                            | 56  |

| UVW                        | 41 | SPI Only                              | 56  |

| FALARM                     | 41 | ABZ and ABZLD                         | 56  |

| ABLIMIT                    | 42 | UVW and UVWLD                         | 56  |

| ZERO0                      | 42 | ABZUVW                                | 57  |

| ZERO1                      | 42 |                                       |     |

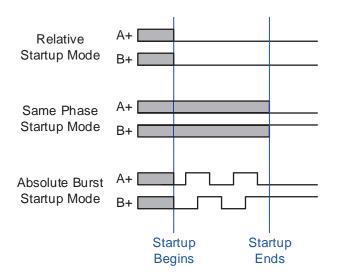

| OUTPUT                     | 42 | STARTUP MODES                         | 58  |

| ZPHASE                     | 44 | STATUS AND FAULT LOGIC                | 59  |

| UVWPH                      | 44 | STATUS AND TAULT LUGIC                | 33  |

| PHASE_LSB                  | 44 | SIN/COS AMPLITUDE MONITOR             | 62  |

| S_ADC                      | 44 |                                       |     |

| C_ADC                      | 44 | EXCESSIVE ERROR DETECTION             | 62  |

| Z_ADC                      | 44 | EXCESSIVE ADAPTION DETECTION          | 63  |

| FILT_CFG                   | 45 | EXCESSIVE ADAPTION DETECTION          | 03  |

| FILT_LAG                   | 45 | DEVICE SERIAL NUMBER AND USER DATA    | 64  |

| FILT_K                     | 45 |                                       |     |

| STAT_CFG                   | 46 | Z TEST MODE AND CALIBRATION           | 65  |

| STAT_VAL                   | 46 | MULTI CYCLE COUNTED                   | 67  |

| STAT_LATCH                 | 47 | MULTI-CYCLE COUNTER                   | 67  |

| STAT_SEL                   | 47 | POSITION CAPTURE                      | 69  |

| STAT_IE                    | 48 |                                       |     |

| STAT_HIZ                   | 48 | FILTER CONFIGURATION                  | 70  |

| STAT_FATAL                 | 48 | CDLONLY OUTDUT MODE                   | 74  |

| EE_ADDR                    | 49 | SPI ONLY OUTPUT MODE                  | 71  |

| EE_DATA                    | 49 | LED INTENSITY CONTROL                 | 72  |

| EE_STAT                    | 49 |                                       |     |

| COMMAND                    | 50 | POST-AB DIVIDER                       | 74  |

| START                      | 51 |                                       |     |

| ADAPT_CFG0                 | 51 | BUSSING MULTIPLE iC-TW28s             | 75  |

| ADAPT_CFG1                 | 52 | CHAINING MULTIPLE iC-TW28s            | 76  |

| SC_AMP_TARG                | 52 |                                       | . 0 |

| SC_AMP_LOW                 | 52 | <b>DESIGN REVIEW: Function Notes</b>  | 77  |

| SC_AMP_HIGH                | 52 |                                       | _   |

| COR Registers              | 52 | REVISION HISTORY                      | 78  |

Rev D5, Page 5/80

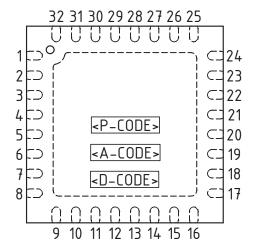

#### **PACKAGING INFORMATION**

#### **PIN CONFIGURATION QFN32-5x5**

(top view)

#### **PIN FUNCTIONS**

|                                              | Name                                                                              | Function                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>4<br>5                                  | SIN+ <sup>3</sup> SIN- <sup>3</sup> AVDD COS+ <sup>3</sup> COS- <sup>3</sup> AVSS | <ul> <li>+ Differential Sine Input</li> <li>- Differential Sine Input</li> <li>+3.3 V Analog Power Supply Input</li> <li>+ Differential Cosine Input</li> <li>- Differential Cosine Input</li> <li>Analog Ground</li> </ul>                                                                                            |

| 7<br>8<br>9<br>10                            | ZERO+ <sup>4</sup><br>ZERO- <sup>3</sup><br>VREF<br>VC<br>Reserved <sup>1</sup>   | + Differential Zero (Index) Input  - Differential Zero (Index) Input ADC Reference Voltage Output Bias Output (VDD/2)                                                                                                                                                                                                  |

| 12<br>13                                     | Reserved <sup>1</sup><br>Reserved <sup>1, 6</sup>                                 |                                                                                                                                                                                                                                                                                                                        |

| 15                                           | xRST <sup>4</sup><br>xCALIB <sup>4</sup><br>xIRQ <sup>4</sup>                     | Reset Input (active low) Auto-Calibration Input (active low) Interrupt Request (active low)                                                                                                                                                                                                                            |

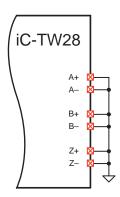

| 17                                           | Z-                                                                                | or Fault Output  - Differential RS422 Z or W Output                                                                                                                                                                                                                                                                    |

| 18                                           | Z+                                                                                | + Differential RS422 Z or W Output                                                                                                                                                                                                                                                                                     |

| 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27 | IOVSS B- B+ IOVDD A- A+ DVDD LED <sup>4</sup> DVSS SO/C3                          | I/O Ground  - Differential RS422 B or V Output  + Differential RS422 B or V Output  +3.3 V I/O Power Supply Input  - Differential RS422 A or U Output  + Differential RS422 A or U Output  +3.3 V Digital Power Supply Input  LED Intensity Control Output  Digital Ground  SPI Slave Output  or Configuration Input 3 |

| 29                                           | SI/C2 <sup>3</sup>                                                                | SPI Slave Input or Configuration Input 2                                                                                                                                                                                                                                                                               |

| 30                                           | SCLK/C1 <sup>3</sup>                                                              | SPI Clock Input or Configuration Input 1                                                                                                                                                                                                                                                                               |

| 31                                           | xSS/C0 <sup>4</sup>                                                               | SPI Slave Select Input or Configuration Input 0                                                                                                                                                                                                                                                                        |

| 32                                           | PINCFG <sup>5, 6</sup>                                                            | Pin Configuration Select Input                                                                                                                                                                                                                                                                                         |

|                                              |                                                                                   |                                                                                                                                                                                                                                                                                                                        |

Backside paddle

IC top marking: <P-CODE> = product code, <A-CODE> = assembly code (subject to changes), <D-CODE> = date code (subject to changes);

$TP^2$

<sup>&</sup>lt;sup>1</sup> Must be connected to ground.

$<sup>^{2}</sup>$  Must be connected to a ground plane at AVSS potential. Can also be used to connect DVSS.

$<sup>^3</sup>$  Connect to ground via  $10\,\text{k}\Omega$  resistor if not used. Do not allow to float.

$<sup>^4</sup>$  Connect to 3.3 V via 10  $k\Omega$  resistor if not used. Do not allow to float.

<sup>&</sup>lt;sup>5</sup> Connect to 3.3 V (to DVDD for pin configuration) or ground (to DVSS for serial configuration). Do not allow to float.

<sup>&</sup>lt;sup>6</sup> Note on compatibility: iC-TW29 uses pin 13 as GPIO, and pin 32 as BISSEN (high selects BiSS).

Rev D5, Page 6/80

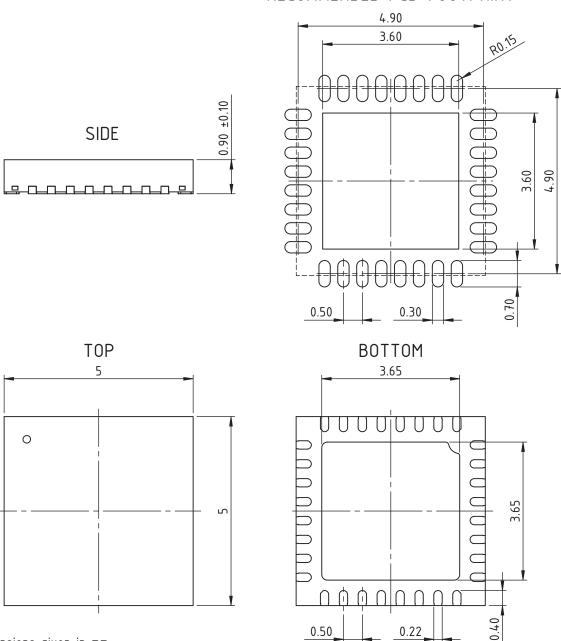

#### **PACKAGE DIMENSIONS**

#### RECOMMENDED PCB-FOOTPRINT

All dimensions given in mm.

Tolerances of form and position according to JEDEC MO-220.

drb\_qfn32-5x5-6\_pack\_1, 10:1

Rev D5, Page 7/80

| NI        | Mama         | 1/0                                    | Function                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|--------------|----------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Name<br>SIN+ | I/O                                    | Function Sine Input +                                | Description CIN CONTROL CONTRO |

| 1<br>2    | SIN+         | Analog in<br>Analog in                 | Sine Input +                                         | Differential sine signal input. For single ended sensors, SIN– must be biased to an appropriate DC level. Do not allow to float.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3         | AVDD         | Supply                                 | Analog Power Supply                                  | +3.1 V to +3.6 V supply input for analog circuitry. AVDD should be tied together with DVDD and IOVDD and supplied from a clean source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4         | COS+         | Analog in                              | Cosine Input +                                       | Differential cosine signal input. For single ended sensors, COS- must                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5         | COS-         | Analog in                              | Cosine Input –                                       | be biased to an appropriate DC level. Do not allow to float.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6         | AVSS         | Ground                                 | Analog Ground                                        | AVSS must be tied to high quality ground, usually a solid PCB plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7         | ZERO+        | Analog in                              | Zero Input +                                         | Differential Zero Gating Input. For single ended sensors, the unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8         | ZERO-        | Analog in                              | Zero Input –                                         | input (either ZERO+ or ZERO-) must be biased to an appropriate DC level. Do not allow to float.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9         | VREF         | Analog out                             | Bias Output                                          | Decouple with 100 nF capacitor to AVSS. Do not inject noise into this pin as it directly impacts ADC conversion quality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10        | VC           | Analog out                             | Bias Output                                          | Decouple with 100 nF capacitor to AVSS. Do not inject noise into this pin as it directly impacts ADC conversion quality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11–<br>13 | Reserved     | Digital inputs                         | Test Inputs                                          | Reserved pins; must be connected to ground for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

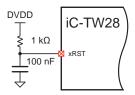

| 14        | xRST         | Digital in, active low                 | Reset Input                                          | The device is reset as long as xRST is low. An external RC network with at least R populated is recommended. Do not allow to float.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15        | xCALIB       | Digital in, active low                 | Calibration Control                                  | Device enters calibration mode on falling edge of CALIB. This pin mus be tied high if not used. Do not allow to float.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16        | xIRQ         | Digital out,<br>active low             | IRQ or Fault Output                                  | Interrupt request output to external micro controller. Output can also be used to directly drive a fault LED in stand-alone applications. Can be configured as push-pull or open-drain. Do not allow to float.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17<br>18  | Z-<br>Z+     | Digital/RS422 out<br>Digital/RS422 out | ·                                                    | In ABZ output mode these are the differential Z outputs. In UVW output mode these are the W outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 19        | IOVSS        | Ground                                 | I/O Ground                                           | All ground pins must be connected to a high quality ground, usually a solid PCB plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 20        | B-           | Digital/RS422 out                      | B– or V– Output                                      | In ABZ output mode these are the differential B outputs. In UVW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 21        | B+           | Digital/RS422 out                      |                                                      | output mode these are the V outputs. In Z calibration mode these show the Z window used to gate the Z output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22        | IOVDD        | Supply                                 | Output Drivers<br>Power Supply                       | +3.1 V to +3.6 V voltage terminal supplying all pin output drivers including the RS422 drivers and LED current.  IOVDD and DVDD must be the same voltage level. IOVDD can require up to 100mA depending on loads. It is usually sufficient to tie IOVDD to the same supply as AVDD and DVDD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | A-           | Digital/RS422 out                      | ·                                                    | In ABZ output mode these are the differential A outputs. In UVW output mode this these are the U outputs. In Z calibration mode these show the un-gated Z signal once per input period. With Encoder Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 24        | A+           | Digital/RS422 out                      | A+or U+ Output                                       | active, A+ is ELCLK input and A- is ELIN input or ELOUT output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 25        | DVDD         | Supply                                 | Digital Power Supply                                 | +3.1 V to +3.6 V supply voltage terminal for digital circuits. DVDD should be tied together with AVDD and IOVDD to a high quality supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 26        | LED          | Digital output                         | LED PWM Output                                       | Used to supply the illumination LED of optical sensors to maintain constant intensity and constant Sin/Cos sensor amplitude. Can be configured as push-pull or open-drain. Do not allow to float.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 27        | DVSS         | Ground                                 | Digital Ground                                       | Pin must tied to high quality ground, usually a solid PCB plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

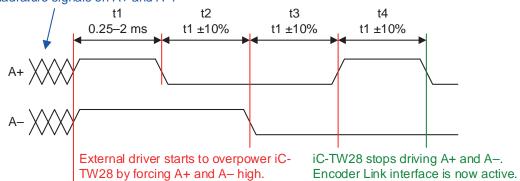

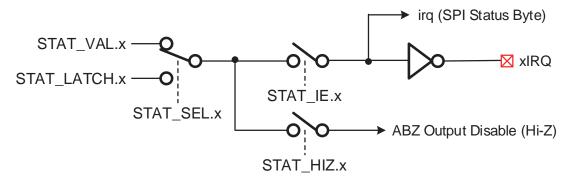

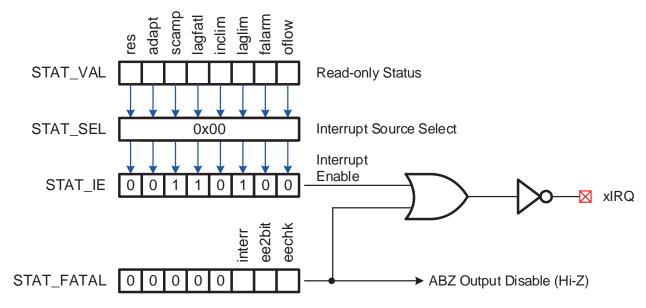

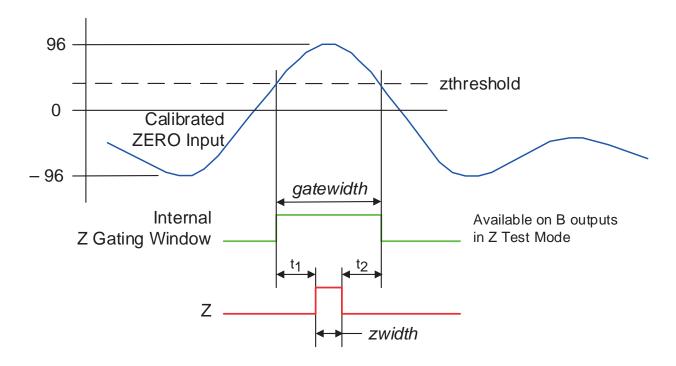

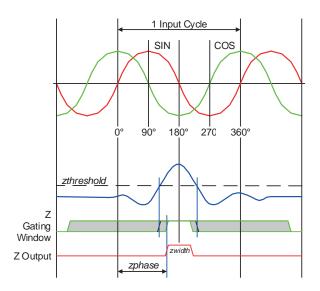

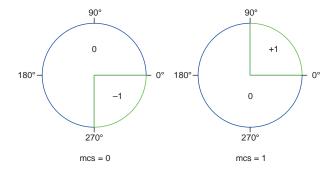

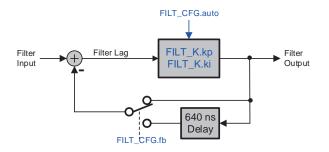

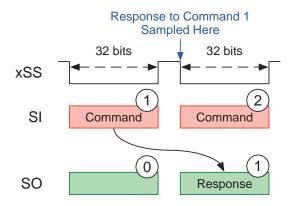

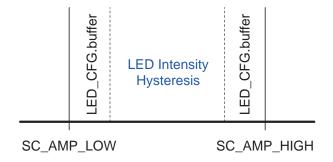

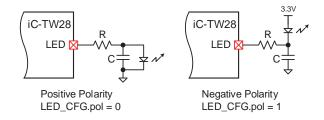

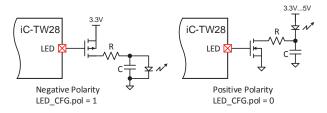

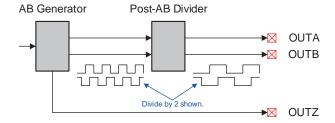

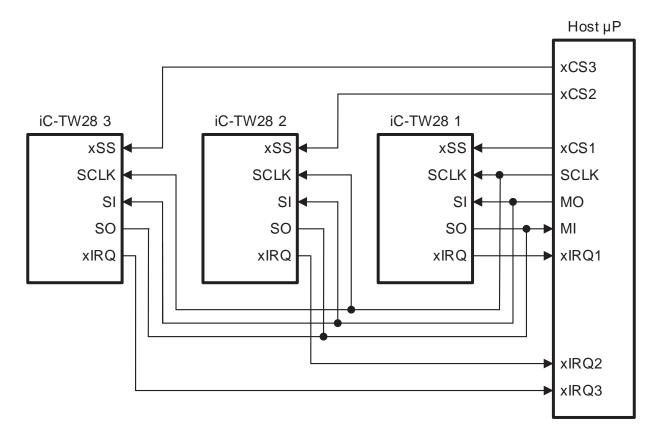

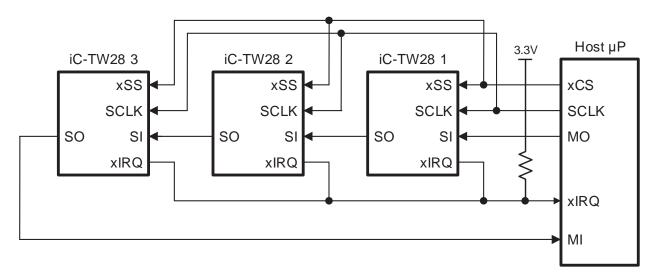

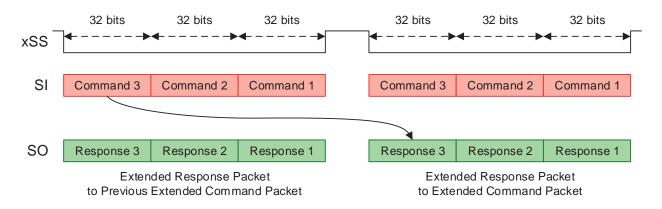

| 28        | SO/C3        | Digital out,<br>Analog in              | SPI Slave Output,<br>Pin Configuration Input 3       | In serial configuration mode, this is the slave output and connects to ar<br>SPI master MI pin. In pin configuration mode, this is input C3. Do not<br>allow to float.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |