Rev A0.9, Page 1/25

### FEATURES

Real-time system for rotation speed up to 120,000 rpm Integrated Hall sensors with automatic offset compensation 4x sensor arrangement for fault-tolerant adjustment Amplitude control for optimum operating point Interpolator with 4096 angular increments/resolution better than 0.1° Programmable resolution, hysteresis, edge spacing, zero position and rotating direction Incremental output of sensor position up to 8 MHz edge rate RS422-compatible AB encoder signals with index Z UVW commutation signals for eight pole EC motor applications Serial interface for data output and configuration SSI-compatible output mode Integrated ZAP diodes for module setup and OEM data, programmable via serial interface Signal error (e.g. magnet loss) can also be read out via serial interface

Analogue sine and cosine differential signals

Extended temperature range from -40 to +125 °C

### APPLICATIONS

Digital angular sensor technology, 0–360° Incremental angular encoder Absolute angular encoder Brushless motors Motor feedback Rotational speed control

Rev A0.9, Page 2/25

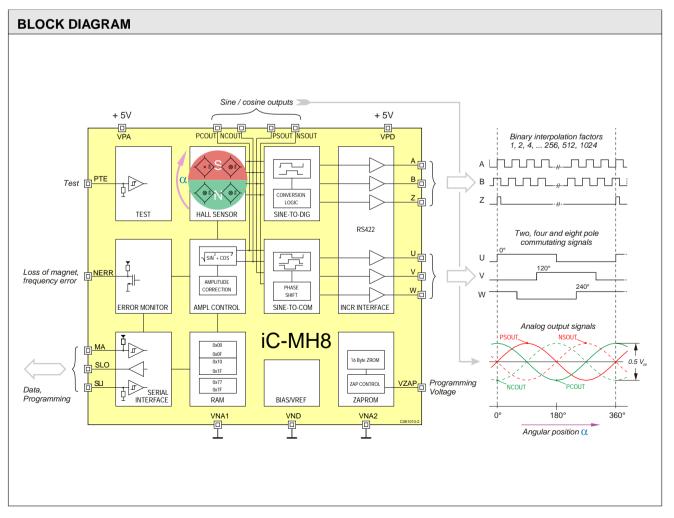

### DESCRIPTION

The iC-MH8 12-bit angular encoder is a position sensor with integrated Hall sensors for scanning a permanent magnet. The signal conditioning unit generates constant-amplitude sine and cosine voltages that can be used for angle calculation. The resolution can be programmed up to a maximum of 4,096 angular increments per rotation.

The integrated serial interface also enables the position data to be read out to several networked sensors. And the integrated memory can be written embedded in the data protocol.

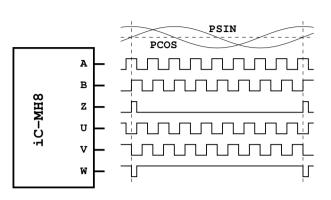

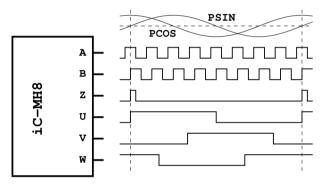

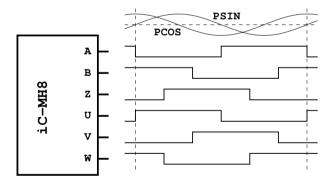

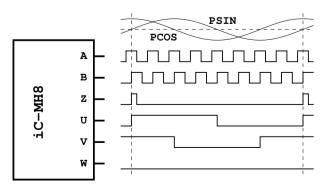

The incremental interface with the pins A, B and Z supplies quadrature signals with an edge rate of up to 8 MHz. Interpolation can be carried out with maximum resolution at a speed of 120,000 rpm. The position of the index pulse Z is adjustable.

The commutation interface with the signals U, V and W provides 120° phase-shifted signals for block commutation of eight pole EC motors. The zero point of the commutation signals is freely definable in increments of 5.625° over 360°.

Sine and cosine signals are externally available to facilitate adjustement.

The RS422-compatible outputs of the incremental interface and the commutation interface are programmable in the output current and the slew rate.

In conjunction with a rotating permanent magnet, the iC-MH8 module forms a one-chip encoder. The entire configuration can be stored in the internal parameter ROM with zapping diodes. The integrated programming algorithm assumes writing of the ROM structure.

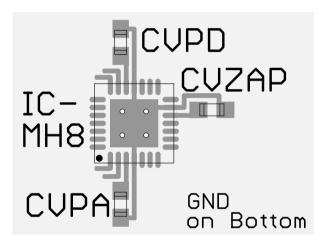

### PACKAGES QFN28 5 x5 mm<sup>2</sup> to JEDEC MO-220-VHHD-1

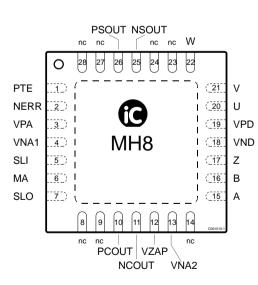

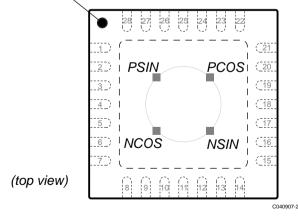

### PIN CONFIGURATION QFN28 5 x 5mm<sup>2</sup>

#### **PIN FUNCTIONS**

- No. Name Function

- 1 PTE Test Enable Pin

- 2 NERR Error output(active low)

#### **PIN FUNCTIONS**

| No.   | Name  | Function                          |

|-------|-------|-----------------------------------|

| 3     | VPA   | +5 V Supply Voltage (analog)      |

| 4     | VNA1  | Ground (analog)                   |

| 5     | SLI   | Serial Interface, Data Input      |

| 6     | MA    | Serial Interface, Clock Input     |

| 7     | SLO   | Serial Interface, Data Output     |

| 8,9   | nc    | not connected                     |

| 10    | PCOUT | Positive Cosine Output            |

| 11    | NCOUT | Negative Cosine Output            |

| 12    | VZAP  | Zener Zapping Programming Voltage |

| 13    | VNA2  | Ground (analog)                   |

| 14    | nc    | not connected                     |

|       | Α     | Incremental A (+NU)               |

|       | В     | Incremental B (+NV)               |

| 17    | Z     | Index Z (+NW)                     |

|       | VND   | Ground (digital)                  |

| 19    | VPD   | +5 V Supply Voltage (digital)     |

| 20    | U     | Commutation U (+NA)               |

| 21    | V     | Commutation V (+NB)               |

|       | W     | Commutation W (+NZ)               |

| 23,24 | nc    | not connected                     |

|       |       | Negative Sine Output              |

|       |       | Positive Sine Output              |

| 27,28 | nc    | not connected                     |

|       | TP    | Thermal-Pad                       |

|       |       |                                   |

The *Thermal Pad* is to be connected to common ground (VNA1, VNA2, VND) on the PCB. Orientation of the logo (**@** MH8 CODE ...) is subject to alteration.

PACKAGE DIMENSIONS

Rev A0.9, Page 3/25

## RECOMMENDED PCB-FOOTPRINT 4.70 3.15 R0.15 SIDE 0.90 З.15 4.70 $\underline{P}$ 0.90 0.30 0.50 TOP BOTTOM 5 3.15 0 $\subset$ 3.15 ഹ ĥ A 0.55 0.50 0.25

drb\_qfn28-2\_pack\_1, 10:1

Rev A0.9, Page 4/25

## **ABSOLUTE MAXIMUM RATINGS**

Beyond these values damage may occur; device operation is not guaranteed.

| ltem | Symbol  | Parameter                                                | Conditions                                |      |      | Unit |

|------|---------|----------------------------------------------------------|-------------------------------------------|------|------|------|

| No.  |         |                                                          |                                           | Min. | Max. |      |

| G001 | V()     | Supply voltages at VPA, VPD                              |                                           | -0.3 | 6    | V    |

| G002 | V(VZAP) | Zapping voltage                                          |                                           | -0.3 | 8    | V    |

| G003 | V()     | Voltages at A, B, Z, U, V, W, MA, SLO,<br>SLI, NERR, PTE |                                           | -0.3 | 6    | V    |

| G004 | I()     | Current in VPA                                           |                                           | -10  | 20   | mA   |

| G005 | I()     | Current in VPD                                           |                                           | -20  | 200  | mA   |

| G006 | I()     | Current in A, B, Z, U, V, W                              |                                           | -100 | 100  | mA   |

| G007 | I()     | Current in MA, SLO, SLI, NERR, PTE                       |                                           | -10  | 10   | mA   |

| G008 | Vd()    | ESD-voltage, all pins                                    | HBM 100 pF discharged over 1.5 k $\Omega$ |      | 2    | kV   |

| G009 | Ts      | Storage temperature                                      |                                           | -40  | 150  | °C   |

| G010 | Tj      | Chip temperature                                         |                                           | -40  | 135  | °C   |

### THERMAL DATA

#### Operating conditions: VPA, VPD = $5V \pm 10\%$

| Item | Symbol | Parameter Conditions                |                                                                                                |      |      |      | Unit |

|------|--------|-------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|------|

| No.  | -      |                                     |                                                                                                | Min. | Тур. | Max. |      |

| T01  | Та     | Operating Ambient Temperature Range |                                                                                                | -40  |      | 125  | °C   |

| T02  | Rthja  |                                     | surface mounted to PCB, <i>thermal pad</i> linked to cooling area of approx. 2 cm <sup>2</sup> |      | 40   |      | K/W  |

Rev A0.9, Page 5/25

## **ELECTRICAL CHARACTERISTICS**

Operating conditions: VPA, VPD =  $5 \vee \pm 10 \%$ , VNA=VND, Ti = -40...125 °C, IBM adjusted to 200 µA , 4 mm NdFeB magnet, unless otherwise noted

| ltem<br>No. | Symbol            | Parameter                                                         | Conditions                                                   | Min.         | Тур. | Max.         | Unit       |

|-------------|-------------------|-------------------------------------------------------------------|--------------------------------------------------------------|--------------|------|--------------|------------|

| Gener       | al                |                                                                   | · · · · · · · · · · · · · · · · · · ·                        |              |      |              |            |

| 001         | V(VPA),<br>V(VPD) | Permissible Supply Voltage                                        |                                                              | 4.5          |      | 5.5          | V          |

| 002         | I(VPA)            | Supply Current in VPA                                             |                                                              | 3            |      | 12           | mA         |

| 003         | I(VPD)            | Supply Current in VPD                                             | PRM = '0', without Load                                      | 5            |      | 27           | mA         |

| 004         | I(VPD)            | Supply Current in VPD                                             | PRM = '1', without Load                                      | 2            |      | 20           | mA         |

| 005         | Vc()hi            | Clamp Voltage hi at MA, SLI,<br>SLO, PTE, NERR                    | Vc()hi = V() - VPD, I() = 1 mA                               | 0.4          |      | 1.5          | V          |

| 006         | Vc()lo            | Clamp Voltage lo at MA, SLI,<br>SLO, PTE, NERR                    | I() = -1 mA                                                  | -1.5         |      | -0.3         | V          |

| Hall S      | ensors and        | Signal Conditioning                                               |                                                              |              |      |              |            |

| 101         | Hext              | Operating Magnetic Field<br>Strength                              | at surface of chip                                           | 20           |      | 100          | kA/m       |

| 102         | fmag              | Operating Magnetic Field<br>Frequency<br>Rotating Speed of Magnet |                                                              |              |      | 2<br>120 000 | kHz<br>rpm |

| 103         | dsens             | Diameter of Hall Sensor Array                                     |                                                              |              | 2    |              | mm         |

| 104         | xdis              | Max. Magnet Axis Displacement vs. Center of Hall Sensor Array     |                                                              |              |      | 0.2          | mm         |

| 105         | xpac              | Chip Placement Error vs. Pack-<br>age                             | with QFN28                                                   | -0.2         |      | 0.2          | mm         |

| 106         | $\phi$ pac        | Chip Tilt Error vs. Package                                       | with QFN28                                                   | -3           |      | +3           | Deg        |

| 107         | hpac              | Sensor-to-Package-Surface Dis-<br>tance                           | with QFN28                                                   |              | 0.4  |              | mm         |

| 108         | Vos               | Trimming range of output offset voltage                           | VOSS or VOSC = 0x7F                                          |              |      | -55          | mV         |

| 109         | Vos               | Trimming range of output offset voltage                           | VOSS or VOSC = 0x3F                                          | 55           |      |              | mV         |

| 110         | Vopt              | Optimal differential output voltage                               | Vopt = Vpp(PSIN) - Vpp(NSIN), ENAC = '0',<br>see Fig. 6      |              | 4    |              | Vpp        |

| 111         | Vratio            | Amplitude Ratio                                                   | Vratio = Vpp(PSIN) / Vpp(PCOS), GCC = 0x3F                   | 1.09         |      |              |            |

| 112         | Vratio            | Amplitude Ratio                                                   | Vratio = Vpp(PSIN) / Vpp(PCOS), GCC = 0x40                   |              |      | 0.92         |            |

| Signa       | I Level Con       | trol                                                              |                                                              |              |      |              |            |

| 201         | Vpp               | Differential Peak-to-Peak Output<br>Amplitude                     | Vpp = Vpk(Px) - Vpk(Nx), ENAC = '1', see Fig.<br>6           | 3.2          |      | 4.8          | Vpp        |

| 202         | ton               | Controller Settling Time                                          | to ±10% of final amplitude                                   |              |      | 300          | μs         |

| 203         | Vt()lo            | MINERR Amplitude Error Thresh-<br>old                             | see 201                                                      | 1.0          |      | 2.8          | Vpp        |

| 204         | Vt()hi            | MAXERR Amplitude Error<br>Threshold                               | see 201                                                      | 4.8          |      | 5.8          | Vpp        |

| Band        | gap Referer       |                                                                   |                                                              |              |      |              |            |

| 401         | Vbg               | Bandgap Reference Voltage                                         |                                                              | 1.18         | 1.25 | 1.32         | V          |

| 402         | Vref              | Reference Voltage                                                 |                                                              | 45           | 50   | 55           | %VPA       |

| 403         | libm              | Bias Current                                                      | CIBM = 0x0<br>CIBM = 0xF<br>Bias Current adjusted            | -370<br>-220 | -200 | -100<br>-180 | μΑ<br>μΑ   |

| 404         | VPDon             | Turn-on Threshold VPD, System                                     | Bias Current adjusted<br>V(VPD) – V(VND), increasing voltage | 3.65         | 4.0  | 4.3          | μA<br>V    |

| 405         | VPDoff            | Turn-off Threshold VPD, System                                    | V(VPD) – V(VND), decreasing voltage                          | 3            | 3.5  | 3.8          | V          |

| 406         | VPDhys            | Hysteresis System on/reset                                        |                                                              | 0.3          |      |              | V          |

Rev A0.9, Page 6/25

## **ELECTRICAL CHARACTERISTICS**

Operating conditions:

VPA, VPD = 5 V ±10 %, VNA=VND, Tj = -40...125 °C, IBM adjusted to 200 µA , 4 mm NdFeB magnet, unless otherwise noted

| ltem<br>No. | Symbol       | Parameter                                  | Conditions                                                                                                                           | Min.  | Тур.        | Max. | Unit       |

|-------------|--------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------|-------------|------|------------|

| 407         | Vosr         | Reference voltage offset com-<br>pensation |                                                                                                                                      | 475   | 500         | 525  | mV         |

| Clock       | Generation   | Ponodion                                   |                                                                                                                                      |       |             |      | <u></u>    |

| 501         | f()sys       | System Clock                               | Bias Current adjusted                                                                                                                | 0.85  | 1.0         | 1.2  | MHz        |

| 502         | f()sdc       | Sinus/Digital-Converter Clock              | Bias Current adjusted                                                                                                                | 13.5  | 16          | 18   | MHz        |

|             | gital Conve  |                                            |                                                                                                                                      | 10.0  |             |      |            |

| 601         | RESsdc       | Sinus/Digital-Converter Resolu-            |                                                                                                                                      |       | 12          |      | Bit        |

| 001         |              | tion                                       |                                                                                                                                      |       |             |      |            |

| 602         | AAabs        | Absolute Angular Accuracy                  | Vpp() = 4 V, adjusted                                                                                                                | -0.35 |             | 0.35 | Deg        |

| 603         | AArel        | Relative Angular Accuracy                  | with reference to an output periode at A, B.<br>CFGRES=0x2, ENF=1, PRM=0, HCLH=1,<br>GAING=0x0, Vpp(SIN/COS) = 4 Vpp.<br>see Fig. 17 |       | ± 10        |      | %          |

| 604         | f()ab        | Output frequency at A, B                   | CFGMTD = 0x0, CFGRES=0x0<br>CFGMTD = 0x7, CFGRES=0x0                                                                                 |       | 2.0<br>0.25 |      | MHz<br>MHz |

| Serial      | Interface, D | igital Outputs MA, SLO, SLI                |                                                                                                                                      |       |             |      |            |

| 701         | Vs(SLO)hi    | Saturation Voltage High                    | V(SLO) = V(VPD) - V(), $ I(SLO) = 4  mA$                                                                                             |       |             | 0.4  | V          |

| 702         | Vs(SLO)lo    | Saturation Voltage Low                     | I(SLO) = 4 mA to VND                                                                                                                 |       |             | 0.4  | V          |

| 703         | Isc(SLO)hi   | Short-Circuit Current High                 | $V(SLO) = V(VND), 25^{\circ}C$                                                                                                       | -90   | -50         |      | mA         |

| 704         | Isc(SLO)lo   | Short-Circuit Current Low                  | V(SLO) = V(VPD), 25°C                                                                                                                |       | 50          | 80   | mA         |

| 705         | tr(SLO)      | Rise Time SLO                              | CL = 50 pF                                                                                                                           |       |             | 60   | ns         |

| 706         | tf(SLO)      | Fall Time SLO                              | CL = 50 pF                                                                                                                           |       |             | 60   | ns         |

| 707         | Vt()hi       | Threshold Voltage High: MA, SLI            | · ·                                                                                                                                  | -     |             | 2    | V          |

| 708         | Vt()lo       | Threshold Voltage Low: MA, SLI             |                                                                                                                                      | 0.8   |             |      | V          |

| 709         | Vt()hys      | Threshold Hysteresis: MA, SLI              |                                                                                                                                      | 140   | 250         |      | mV         |

| 710         | lpd()        | Pull-Down Current: MA, SLI                 | V() = 0VPD - 1 V                                                                                                                     | 6     | 30          | 60   | μA         |

| 711         | Ipu(MA)      |                                            |                                                                                                                                      | -60   | -30         | -6   | μA         |

| 712         | f(MA)        |                                            |                                                                                                                                      |       |             | 10   | MHz        |

| Zappi       | ng and Test  | 1                                          | 1                                                                                                                                    | Ш     |             | I    |            |

| 801         | Vt()hi       | Threshold Voltage High VZAP,<br>PTE        | with reference to VND                                                                                                                |       |             | 2    | V          |

| 802         | Vt()lo       | Threshold Voltage Low VZAP,<br>PTE         | with reference to VND                                                                                                                | 0.8   |             |      | V          |

| 803         | Vt()hys      | Hysteresis                                 | Vt()hys = Vt()hi – Vt()lo                                                                                                            | 140   | 250         |      | mV         |

| 804         | Vt()nozap    | Threshold Voltage Nozap VZAP               | $V() = V(VZAP) - V(VPA), V(VPA) = 5 V \pm 5 \%,$<br>at chip temperature 27 °C                                                        | 0.7   |             |      | V          |

| 805         | Vt()zap      | Threshold Voltage Zap VZAP                 | $V() = V(VZAP) - V(VPA), V(VPA) = 5 V \pm 5 \%,$<br>at chip temperature 27 °C                                                        |       |             | 1.2  | V          |

| 806         | V()zap       | Zapping voltage                            | PROG = '1'                                                                                                                           | 6.9   | 7.0         | 7.1  | V          |

| 807         | V()zpd       | Diode voltage, zapped                      |                                                                                                                                      |       |             | 2    | V          |

| 808         | V()uzpd      | Diode voltage, unzapped                    |                                                                                                                                      | 3     |             |      | V          |

| 809         | Rpd()VZAP    |                                            |                                                                                                                                      | 30    |             | 55   | kΩ         |

| NERR        | Output       | 1                                          | 1                                                                                                                                    |       |             |      | L          |

| 901         | Vt()hi       | Input Threshold Voltage High               | with reference to VND                                                                                                                |       |             | 2    | V          |

| 902         | Vs()lo       | Saturation Voltage Low                     | I() = 4 mA , with reference to VND                                                                                                   |       |             | 0.4  | V          |

| 903         | Vt()lo       | Input Threshold Voltage Low                | with reference to VND                                                                                                                | 0.8   |             |      | V          |

| 904         | Vt()hys      | Input Hysteresis                           | Vt()hys = Vt()hi - Vt()lo                                                                                                            | 140   | 250         |      | mV         |

| 905         | lpu()        | Pull-up Current Source                     | V(NERR) = 0VPD - 1 V                                                                                                                 | -800  | -300        | -80  | μA         |

| 906         | lsc()lo      | Short circuit current Lo                   | $V(NERR) = V(VPD), Tj = 25^{\circ}C$                                                                                                 |       | 50          | 80   | mA         |

| 907         | tf()hilo     | Decay time                                 | CL = 50 pF                                                                                                                           |       |             | 60   | ns         |

Rev A0.9, Page 7/25

## **ELECTRICAL CHARACTERISTICS**

Operating conditions:

| tem<br>No. | Symbol     | Parameter                    | Conditions                                                                                                                                                                                 | Min.                       | Тур. | Max.                     | Unit                 |

|------------|------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|--------------------------|----------------------|

| Digita     | Line Drive | er Outputs                   |                                                                                                                                                                                            |                            |      |                          |                      |

| P01        | Vs()hi     | Saturation Voltage hi        | $\begin{array}{l} Vs() = VPD - V();\\ CfgDR(1:0) = 00, I() = -4  mA\\ CfgDR(1:0) = 01, I() = -50  mA\\ CfgDR(1:0) = 10, I() = -50  mA\\ CfgDR(1:0) = 11, I() = -20  mA\\ \end{array}$      |                            |      | 200<br>700<br>700<br>400 | mV<br>mV<br>mV<br>mV |

| P02        | Vs()lo     | Saturation Voltage lo        | CfgDR(1:0) = 00, I() = $-4 \text{ mA}$<br>CfgDR(1:0) = 01, I() = $-50 \text{ mA}$<br>CfgDR(1:0) = 10, I() = $-50 \text{ mA}$<br>CfgDR(1:0) = 11, I() = $-20 \text{ mA}$                    |                            |      | 200<br>700<br>700<br>400 | mV<br>mV<br>mV<br>mV |

| P03        | Isc()hi    | Short-Circuit Current hi     | V() = 0 V;<br>CfgDR(1:0) = 00<br>CfgDR(1:0) = 01<br>CfgDR(1:0) = 10<br>CfgDR(1:0) = 11                                                                                                     | -12<br>-125<br>-125<br>-60 |      | -4<br>-50<br>-50<br>-20  | mA<br>mA<br>mA<br>mA |

| P04        | Isc()lo    | Short-Circuit Current lo     | V() = VPD;CfgDR(1:0) = 00CfgDR(1:0) = 01CfgDR(1:0) = 10CfgDR(1:0) = 11                                                                                                                     | 4<br>50<br>50<br>20        |      | 12<br>125<br>125<br>60   | mA<br>mA<br>mA<br>mA |

| P05        | llk()tri   | Leakage Current Tristate     | TRIHL(1:0) = 11                                                                                                                                                                            | -100                       |      | 100                      | μA                   |

| P06        | tr()       | Rise-Time lo to hi at Q      | RL = $100 \Omega$ to VND;<br>CfgDR(1:0) = 00<br>CfgDR(1:0) = 01<br>CfgDR(1:0) = 10<br>CfgDR(1:0) = 11                                                                                      | 5<br>5<br>50<br>5          |      | 20<br>20<br>350<br>40    | ns<br>ns<br>ns<br>ns |

| P07        | tf()       | Fall-Time hi to lo at Q      | $ \begin{array}{l} \text{RL} = 100  \Omega \ \text{to} \ \text{VND}; \\ \text{CfgDR}(1:0) = 00 \\ \text{CfgDR}(1:0) = 01 \\ \text{CfgDR}(1:0) = 10 \\ \text{CfgDR}(1:0) = 11 \end{array} $ | 5<br>5<br>50<br>5          |      | 20<br>20<br>350<br>40    | ns<br>ns<br>ns<br>ns |

| Analo      | g Outputs  | PSOUT, NSOUT, PCOUT, NCOUT   |                                                                                                                                                                                            |                            |      |                          |                      |

| Q01        | Vpk()      | Max. Output Signal Amplitude | RI = 50 $\Omega$ vs. VPD / 2, see Fig.                                                                                                                                                     | 200                        |      | 300                      | mV                   |

| Q02        | Vos()      | Output Offset Voltage        |                                                                                                                                                                                            |                            | ±200 |                          | μV                   |

| Q03        | fc()       | Output Cut-off Frequency     | Cl = 250 pF                                                                                                                                                                                | 10                         |      |                          | kHz                  |

| Q04        | lsc()hi,lo | Output Short-circuit Current | pin shorten to VPD or VND                                                                                                                                                                  | 10                         |      | 50                       | mA                   |

Rev A0.9, Page 8/25

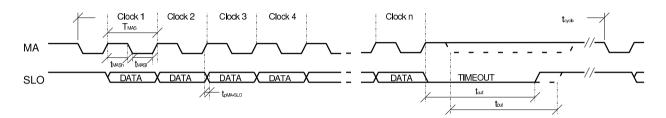

### **OPERATING REQUIREMENTS: Serial Interface**

Operating conditions: VPA, VPD = 5 V  $\pm$ 10 %, Ta = -40...125 °C, IBM calibrated to 200  $\mu$ A; Logic levels referenced to VND: lo = 0...0.45 V, hi = 2.4 V...VPD

| Item Symbol |                   | Parameter                      | Conditions                |      |                     |    |  |

|-------------|-------------------|--------------------------------|---------------------------|------|---------------------|----|--|

| No.         |                   |                                |                           | Min. | Max.                |    |  |

| SSI Pro     | otocol (EN        | SSI = 1)                       |                           |      |                     |    |  |

| 1001        | T <sub>MAS</sub>  | Permissible Clock Period       | tout determined by CFGTOS | 250  | 2x t <sub>out</sub> | ns |  |

| 1002        | t <sub>MASh</sub> | Clock Signal Hi Level Duration |                           | 25   | t <sub>out</sub>    | ns |  |

| 1003        | t <sub>MASI</sub> | Clock Signal Lo Level Duration |                           | 25   | t <sub>out</sub>    | ns |  |

Figure 1: I/O Interface timing with SSI protocol

Rev A0.9, Page 9/25

## Registers

| OVERV                 | IEW                     |              |                |                   |              |           |         |         |  |

|-----------------------|-------------------------|--------------|----------------|-------------------|--------------|-----------|---------|---------|--|

| Adr                   | Bit 7                   | Bit 6        | Bit 5          | Bit 4             | Bit 3        | Bit 2     | Bit 1   | Bit 0   |  |

| Hall Sig              | nal Condition           | ing          |                | 1                 | 1            |           |         |         |  |

| 0x00 z                | z GAING(1:0) GAINF(5:0) |              |                |                   |              |           |         |         |  |

| 0x01 z                | ENAC                    |              |                |                   | GCC(6:0)     |           |         |         |  |

| 0x02 z                | 1                       |              |                |                   | VOSS(6:0)    |           |         |         |  |

| 0x03 z                | PRM                     |              |                |                   | VOSC(6:0)    |           |         |         |  |

| 0x04 z                | HCLH                    | DPU          | DAO            | CFGTOB            |              | CIBM      | 1(3:0)  |         |  |

| RS422 D               | Driver                  |              |                |                   |              |           |         |         |  |

| 0x05 z                | ENSSI                   | CFGPROT      | CFG            | D(1:0)            | TRIH         | L(1:0)    | CFGD    | R(1:0)  |  |

| Sine/Dig              | ital Converte           | r            |                |                   |              |           |         |         |  |

| 0x06 z                | ENF                     |              | CFGMTD(2:0)    |                   |              | CFGR      | ES(3:0) |         |  |

| 0x07 z                |                         |              |                |                   | OS(7:0)      |           |         |         |  |

| 0x08 z                | CFGH                    | YS(1:0)      | CFGDIR         | CFGSU             |              | DLE(1:0)  | CFGA    | B(1:0)  |  |

| 0x09 z                |                         |              |                | CfgCC             | OM(7:0)      |           |         |         |  |

| 0x0A z                |                         |              |                |                   | -            |           |         |         |  |

| 0x0B z                |                         |              |                |                   | -            |           |         |         |  |

| 0x0C z                |                         |              |                |                   | -            |           |         |         |  |

| 0x0D                  |                         |              |                |                   | -            |           |         |         |  |

| Test set              | tings                   |              |                |                   | F(7.0)       |           |         |         |  |

| 0x0E <i>p</i><br>0x0F | ENHC                    | r00          | <b>r</b> 00    | TES               |              | r00       | r00     | PROGZAP |  |

|                       |                         | res.         | res.           | res.              | res.         | res.      | res.    | FRUGZAF |  |

|                       | des (read only          | y)           | ZAD diada      | s for addresses ( | woo ovoc and |           |         |         |  |

| 0x10<br>              |                         |              | ZAP diodes     |                   |              | UX7DUX7F  |         |         |  |

| 0x1F                  |                         |              |                |                   |              |           |         |         |  |

| not used              | d                       |              |                |                   |              |           |         |         |  |

| 0x20                  |                         |              |                | 'invalid a        | dresses'     |           |         |         |  |

| <br>0x41              |                         |              |                |                   |              |           |         |         |  |

| Profile i             | dentification (         | read only)   |                |                   |              |           |         |         |  |

| 0x42                  |                         |              |                | Profile           | - 0x2C       |           |         |         |  |

| 0x43                  |                         | Profile      | e - 0x0        |                   |              | Data lenç | th DLEN |         |  |

| not used              | d                       |              |                |                   |              |           |         |         |  |

| 0x44                  |                         |              |                | 'invalid          | adress'      |           |         |         |  |

| <br>0x75              |                         |              |                |                   |              |           |         |         |  |

| Status n              | nessages (rea           | d only; mess | ages will be s | et back durin     | g reading)   |           |         |         |  |

| 0x76                  |                         |              |                | GA                | AIN          |           |         |         |  |

|                       | PROGERR                 | ERRSDATA     | ERRAMIN        | ERRAMAX           | ERREXT       | res.      | res.    | PROGOK  |  |

## Rev A0.9, Page 10/25

| OVERV     | RVIEW          |                                                                                                         |  |             |              |  |  |  |  |  |

|-----------|----------------|---------------------------------------------------------------------------------------------------------|--|-------------|--------------|--|--|--|--|--|

| Adr       | Bit 7          | Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0 |  |             |              |  |  |  |  |  |

| Identific | ation (0x78 bi | tion (0x78 bis 0x7B read-only)                                                                          |  |             |              |  |  |  |  |  |

| 0x78      |                |                                                                                                         |  | Device ID - | 0x4D ('M')   |  |  |  |  |  |

| 0x79      |                |                                                                                                         |  | Device ID · | - 0x48 ('H') |  |  |  |  |  |

| 0x7A      |                | Revision - 0x38 ('8')                                                                                   |  |             |              |  |  |  |  |  |

| 0x7B      |                |                                                                                                         |  | Revision    | - 0x00 (")   |  |  |  |  |  |

| 0x7C      |                | - CFGTOS                                                                                                |  |             |              |  |  |  |  |  |

| 0x7D z    |                | Manufacturer Revision - 0x00                                                                            |  |             |              |  |  |  |  |  |

| 0x7E z    |                | Manufacturer ID - 0x00                                                                                  |  |             |              |  |  |  |  |  |

| 0x7F z    |                | Manufacturer ID - 0x00                                                                                  |  |             |              |  |  |  |  |  |

z: Register value programmable by zapping

p: Register value write protected; can only be changed while V(VZAP)> Vt()hi

Table 5: Register layout

| Hall signal pr | ocessing Page 12                      | Sine/digital c | onverter Page 18                     |

|----------------|---------------------------------------|----------------|--------------------------------------|

| GAING:         | Hall signal amplification range       | CFGRES:        | Resolution of sine digital converter |

| GAINF:         | Hall signal amplification (1-20, log. | CFGZPOS:       | Zero point for position              |

|                | scale)                                | CFGAB:         | Configuration of incremental output  |

| GCC:           | Amplification calibration cosine      | CFGPOLE:       | No. of poles for commutation signals |

| ENAC:          | Activation of amplitude control       | CFGSU:         | Behavior during start-up             |

| VOSS:          | Offset calibration sine               | CFGMTD:        | Frequency at AB                      |

| VOSC:          | Offset calibration cosine             | CFGDIR:        | Rotating direction reversal          |

| PRM:           | Energy-saving mode                    | CFGHYS:        | Hysteresis sine/digital converter    |

| CIBM:          | Calibration of bias current           | CFGCOM:        | Zero point for commutation           |

| DPU            | Deactivation of NERR pull-up          |                |                                      |

| HCLH           | Activation of high Hall clock pulse   | Test           |                                      |

| ENF            | Activation of noise filter            | TEST:          | Test mode                            |

| DAO:           | Disable Analog Outputs                | ENHC:          | Enable High Current during ZAP-      |

|                |                                       |                | Diode Read (iC-MH82 and later)       |

| RS422 driver   | Page 21                               | PROGZAP:       | Activation of programming routine    |

| CFGDR:         | Driver property                       |                |                                      |

| TRIHL:         | Tristate high-side/low-side driver    |                |                                      |

| CFGO:          | Configuration of output mode          |                |                                      |

| CFGPROT:       | Write/read protection memory          |                |                                      |

| ENSSI:         | Activation of SSI mode                |                |                                      |

Rev A0.9, Page 11/25

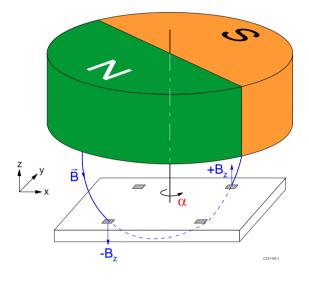

### Sensor principle

Figure 2: Sensor principle

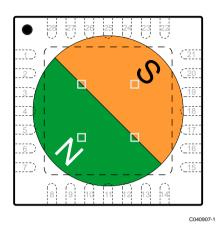

In conjunction with a rotating permanent magnet, the iC-MH8 module can be used to create a complete encoder system. A diametrically magnetized, cylindrical permanent magnet made of neodymium iron boron (NdFeB) or samarium cobalt (SmCo) generates optimum sensor signals. The diameter of the magnet should be in the range of 3 to 6 mm.

The iC-MH8 has four Hall sensors adapted for angle determination and to convert the magnetic field into a measurable Hall voltage. Only the z-component of the magnetic field is evaluated, whereby the field lines pass through two opposing Hall sensors in the opposite direction. Figure 2 shows an example of field vectors. The arrangement of the Hall sensors is selected so that the mounting of the magnets relative to iC-MH8 is extremely tolerant. Two Hall sensors combined provide a differential Hall signal. When the magnet is rotated around the longitudinal axis, sine and cosine output voltages are produced which can be used to determine angles.

### Position of the Hall sensors and the analog sensor signal

The Hall sensors are placed in the center of the QFN28 package at 90° to one another and arranged in a circle with a diameter of 2 mm as shown in Figure 3.

Figure 3: Position of the Hall sensors

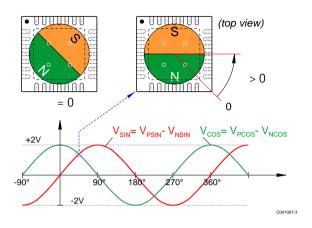

When a magnetic south pole comes close to the surface of the package the resulting magnetic field has a positive component in the +z direction (i.e. from the top of the package) and the individual Hall sensors each generate their own positive signal voltage. In order to calculate the angle position of a diametrically polarized magnet placed above the device a difference in signal is formed between opposite pairs of Hall sensors, resulting in the sine being  $V_{SIN} = V_{PSIN} - V_{NSIN}$  and the cosine  $V_{COS} = V_{PCOS} - V_{NCOS}$ . The zero angle position of the magnet is marked by the resulting cosine voltage value being at a maximum and the sine voltage value at zero.

This is the case when the south pole of the magnet is exactly above the PCOS sensor and the north pole is above sensor NCOS, as shown in Figure 4. Sensors PSIN and NSIN are placed along the pole boundary so that neither generate a Hall signal.

When the magnet is rotated counterclockwise the poles then also cover the PSIN and NSIN sensors, resulting in the sine and cosine signals shown in Figure 5 being produced.

### Rev A0.9, Page 12/25

Figure 4: Zero position of the magnet

Figure 5: Pattern of the analog sensor signals with the angle of rotation

### Hall Signal Processing

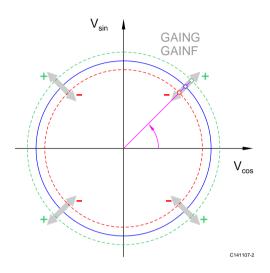

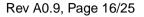

The iC-MH8 module has a signal calibration function that can compensate for the signal and adjustment errors. The Hall signals are amplified in two steps. First, the range of the field strength within which the Hall sensor is operated must be roughly selected. The first amplifier stage can be programmed in the following ranges:

| GAING(1:0) | Addr. 0x00; bit 7:6 |

|------------|---------------------|

| 00         | 5-fold              |

| 01         | 10-fold             |

| 10         | 15-fold             |

| 11         | 20-fold             |

Table 6: Range selection for Hall signal amplification

The operating range can be specified in advance in accordance with the temperature coefficient and the magnet distance. The integrated amplitude control can correct the signal amplitude between 1 and 20 via another amplification factor. Should the control reach the range limits, a different signal amplification must be selected via GAING.

| GAINF(5:0) | Addr. 0x00; bit 5:0                     |

|------------|-----------------------------------------|

| 0x00       |                                         |

|            | 1,000                                   |

| 0x02       |                                         |

| 0x03       | 1,048                                   |

|            | $exp(rac{ln(20)}{64} \cdot GAINF - 2)$ |

| 0x3F       | 17,38                                   |

Table 7: Hall signal amplification

The second amplifier stage can be varied in an additional range. With the amplitude control (ENAC = '0') deactivated, the amplification in the GAINF register is used. With the amplitude control (ENAC = '1') activated, the GAINF register bits have no effect.

| GCC(6:0) | Addr. 0x01; bit 6:0                           |

|----------|-----------------------------------------------|

| 0x00     | 1,000                                         |

| 0x01     | 1,0015                                        |

|          | $exp(\frac{ln(20)}{2048} \cdot GCC)$          |

| 0x3F     | 1,0965                                        |

| 0x40     | 0,9106                                        |

|          | $exp(-\frac{ln(20)}{2048} \cdot (128 - GCC))$ |

| 0x7F     | 0,9985                                        |

Table 8: Amplification calibration cosine

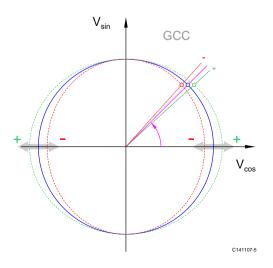

The GCC register is used to correct the sensitivity of the sine channel in relation to the cosine channel. The cosine amplitude can be corrected within a range of approximately  $\pm 10\%$ .

| ENAC | Addr. 0x01; bit 7             |

|------|-------------------------------|

| 0    | amplitude control deactivated |

| 1    | amplitude control active      |

Table 9: Activation of amplitude control

The integrated amplitude control can be activated with the ENAC bit. In this case the differential signal amplitude is adjusted to 4 Vss and the values of GAINF have no effect here.

PSIN-NSIN PCOS-NCOS 4Vss

Figure 6: Definition of differential amplitude

After switch-on the amplification is increased until the setpoint amplitude is reached. The amplification is automatically corrected in case of a change in the input amplitude by increasing the distance between the magnet and the sensor, in case of a change in the supply voltage or a temperature change. The sine signals are therefore always converted into high-resolution quadrature signals at the optimum amplitude.

| VOSS(6:0) | Addr. 0x02; bit 6:0 |

|-----------|---------------------|

| VOSC(6:0) | Addr. 0x03; bit 6:0 |

| 0x00      | 0 mV                |

| 0x01      | 1 mV                |

|           |                     |

| 0x3F      | 63 mV               |

| 0x40      | 0 mV                |

| 0x41      | -1 mV               |

|           |                     |

| 0x7F      | -63 mV              |

Table 10: Offset calibration for sine and cosine

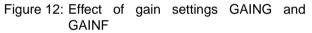

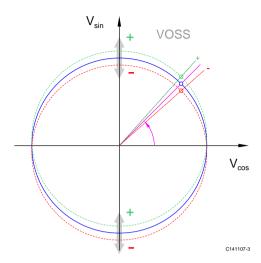

Should there be an offset in the sine or cosine signal that, among other things, can also be caused by an inexactly adjusted magnet, then this offset can be corrected by the VOSS and VOSC registers. The output voltage can be shifted by  $\pm 63$  mV in each case to compensate for the offset.

Rev A0.9, Page 13/25

| PRM | Addr. 0x03; bit 7              |

|-----|--------------------------------|

| 0   | Energy-saving mode deactivated |

| 1   | Energy-saving mode active      |

Table 11: Energy-saving mode

In the energy-saving mode the current consumption of the Hall sensors can be quartered. This also reduces the maximum rotating frequency by a factor of 4.

| CIBM(3:0) | Addr. 0x04; bit 3:0 |

|-----------|---------------------|

| 0x0       | -40 %               |

|           |                     |

| 0x8       | 0%                  |

| 0x9       | +5 %                |

|           |                     |

| 0xF       | +35 %               |

Table 12: Calibration of bias current

The bias current is factory calibrated to  $200 \,\mu$ A. The calibration can be verified in test mode (TEST = 0x43) by measuring the current from Pin B to Pin VNA.

| HCLH | Addr. 0x04; bit 7 |

|------|-------------------|

| 0    | 250 kHz           |

| 1    | 500 kHz           |

Table 13: Activation of high Hall clock pulse

The switching-current hall sensors can be operated at two frequencies. At 500 kHz the sine has twice the number of support points. This setting is of interest at high speeds above 30,000 rpm.

Rev A0.9, Page 14/25

#### Test modes for signal calibration

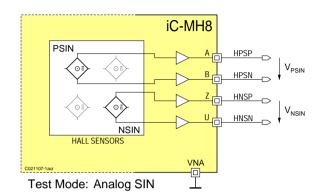

For signal calibration iC-MH8 has several test settings which make internal reference quantities and the amplified Hall voltages of the individual sensors accessible at external pins A, B, Z and U for measurement purposes. This enables the settings of the offset (VOSS, VOSC), gain (GAING, GAINF) and amplitude ratio of the cosine to the sine signal (GCC) to be directly observed on the oscilloscope.

Test mode can be triggered by connecting pin VZAP to VPD and programming the TEST register (address 0x0E). The individual test modes are listed in the following table:

| Output signals in test mode |      |       |       |       |       |

|-----------------------------|------|-------|-------|-------|-------|

| Mode                        | TEST | Pin A | Pin B | Pin Z | Pin U |

| Normal                      | 0x00 | A     | В     | Z     | U     |

| Analog SIN                  | 0x20 | HPSP  | HPSN  | HNSP  | HNSN  |

| Analog COS                  | 0x21 | HPCP  | HPCN  | HNCP  | HNCN  |

| Analog OUT                  | 0x22 | PSIN  | NSIN  | PCOS  | NCOS  |

| Analog REF                  | 0x43 | VREF  | IBM   | VBG   | VOSR  |

| Digital CLK                 | 0xC0 | CLKD  |       |       |       |

Table 14: Test modes and available output signals

The output voltages are provided as differential signals with an average voltage of 2.5 V. The gain is determined by register values GAING and GAINF and should be set so that output amplitudes from the sine and cosine signals of about 1 V are visible.

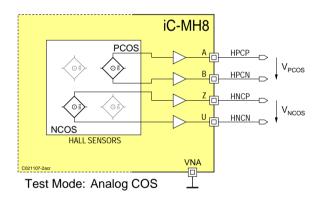

#### **Test modes Analog SIN and Analog COS**

In these test modes it is possible to measure the signals from the individual Hall sensors independent of one another. The name of the signal is derived from the sensor name and position. **HPSP**, for example, is the (amplified) Hall voltage of sensor **PSIN** at the **p**ositive signal path; similarly, **HNCN** is the Hall voltage of sensor **NC**OS at the **n**egative signal path. The effective Hall voltage is accrued from the differential voltage between the positive and negative signal paths of the respective sensor.

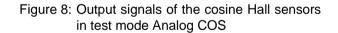

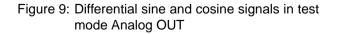

### Test mode Analog OUT

In this test mode the sensor signals are available at the outputs as they would be when present internally for further processing on the interpolator. The interpolation accuracy which can be obtained is determined by the quality of signals  $V_{sin}$  and  $V_{cos}$  and can be influenced in this particular test mode by the calibration of the offset, gain and amplitude ratio.

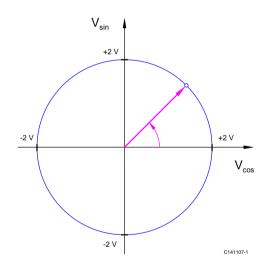

#### Test mode Analog REF

In this mode various internal reference voltages are provided. VREF is equivalent to half the supply voltage (typically 2.5 V) and is used as a reference voltage for

the Hall sensor signals. VBG is the internal bandgap reference (1.24 V), with VOSR (0.5 V) used to generate the range of the offset settings. Bias current IBM determines the internal current setting of the analog circuitry. In order to compensate for variations in this current and thus discrepancies in the characteristics of the individual iC-MH8 devices (due to fluctuations in production, for example), this can be set within a range of -40% to +35% using register parameter CIBM. The nominal value of 200 µA is measured as a short-circuit current at pin B to ground.

#### Test mode Digital CLK

If, due to external circuitry, it is not possible to measure IBM directly, by way of an alternative clock signal CLKD at pin A can be calibrated to a nominal 1 MHz in this test mode via register value CIBM.

#### **Calibration procedure**

The calibration procedure described in the following applies to the optional setting of the internal analog sine and cosine signals and the mechanical adjustment of the magnet and iC-MH8 in relation to one another.

#### **BIAS SETTING**

The BIAS setting compensates for possible manufacturing tolerances in the iC-MH8 devices. A magnetic field does not need to be present for this setting which can thus be made either prior to or during the assembly of magnet and iC-MH8.

If the optional setup process is not used, register CIBM should be set to an average value of 0x8 (which is equivalent to a change of 0%). As described in the previous section, by altering the value in register CIBM in test mode Analog REF current IBM is set to 200 µA or, alternatively, in test mode Digital CLK signal CLKD is set to 1 MHz.

### **MECHANICAL ADJUSTMENT**

iC-MH8 can be adjusted in relation to the magnet in test modes Analog SIN and Analog COS, in which the Hall signals of the individual Hall sensors can be observed while the magnet rotates.

In test mode Analog SIN the output signals of the sine Hall sensors which are diagonally opposite one another are visible at pins A, B, Z and U. iC-MH8 and the magnet are then adjusted in such a way that differential signals  $V_{PSIN}$  and  $V_{NSIN}$  have the same amplitude and a phase shift of 180°. The same applies to test mode Analog COS, where differential signals  $V_{PCOS}$  and  $V_{NCOS}$  are calibrated in the same manner.

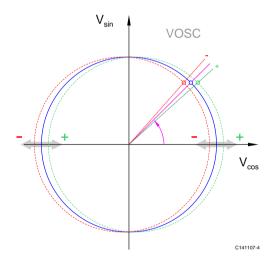

Figure 11: Ideal Lissajous curve

#### CALIBRATION USING ANALOG SIGNALS

In test mode Analog OUT as shown in Figure 5 the internal signals which are transmitted to the sine/digital converter can be tapped with high impedance. With a rotating magnet it is then possible to portray the differential signals V<sub>SIN</sub> and V<sub>COS</sub> as an x-y graph (Lissajous curve) with the help of an oscilloscope. In an ideal setup the sine and cosine analog values describe a perfect circle as a Lissajous curve, as illustrated by Figure 11.

At room temperature and with the amplitude control switched off (ENAC = 0) a rough GAING setting is selected so that at an average fine gain of GAINF = 0x20(a gain factor of ca. 4.5) the Hall signal amplitudes are as close to 1 V as possible. The amplitude can then

Rev A0.9, Page 15/25

preliminary

Figure 10: Setting bias current IBM in test mode Analog REF

laus

be set more accurately by varying GAINF. Variations in the gain factor, as shown in Figure 12, have no effect on the Lissajous curve, enabling the angle information for the interpolator to be maintained.

Deviations of the observed Lissajous curve from the ideal circle can be corrected by varying the amplitude offset (register VOSS, VOSC) and amplitude ratio (register GCC). Changes in these parameters are described in the following figures 13 to 15. Each of these settings has a different effect on the interpolated angle value. A change in the sine offset thus has a maximum effect on the angle value at 0° and 180°, with no alterations whatsoever taking place at angles of 90° and 270°. When varying the cosine offset exactly the opposite can be achieved as these angle pairs can be set independent of one another. Setting the cosine/sine amplitude ratio does not change these angles (0°, 90°, 180° and 270°); however, in-between values of 45°, 135°, 225° and 315° can still be influenced by this parameter.

Once calibration has been carried out a signal such as the one illustrated in Figure 11 should be available.

In the final stage of the process the amplitude control can be switched back on (ENAC =1) to enable deviations in the signal amplitude caused by variations in the magnetic field due to changes in distance and temperature to be automatically controlled.

Figure 13: Effect of the sine offset setting

Figure 14: Effect of the cosine offset setting

Figure 15: Effect of the amplitude ratio

### CALIBRATION USING INCREMENTAL SIGNALS

If test mode cannot be used, signals can also be calibrated using the incremental signals or the values read out serially. In order to achieve a clear relationship between the calibration parameters which have an effect on the analog sensor signals and the digital sensor values derived from these, the position of the zero pulse should be set to ZPOS = 0x0 and the rotating direction should be set to CFGDIR=0, so that the digital signal starting point matches that of the analog signals.

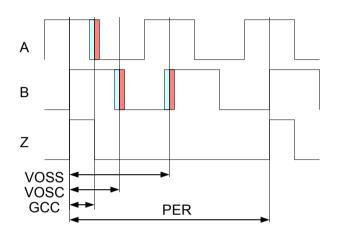

At an incremental resolution of 8 edges per revolution (CFGRES = 0x1) those angle values can be displayed at which calibration parameters VOSS, VOSC and GCC demonstrate their greatest effect. When rotating the magnet at a constant angular speed the incremental signals shown in Figure 16 are achieved, with which the individual edges ideally succeed one another at a temporal distance of an eighth of a cycle (a 45° angle distance). Alternatively, the angle position of the magnet can also be determined using a reference encoder, rendering an even rotational action unnecessary and allowing calibration to be performed using the available set angle values .

The various possible effects of parameters VOSS, VOSC and GCC on the flank position of incremental signals A and B are shown in Figure 16. Ideally, the

Rev A0.9, Page 17/25

distance of the rising edge (equivalent to angle positions of 0° and 180°) at signal A should be exactly half a period (PER). Should the edges deviate from this in distance, the offset of the sine channel can be adjusted using VOSS. The same applies to the falling edges of the A signal which should also have a distance of half a period; deviations can be calibrated using the offset of cosine parameter VOSC. With parameter GCC the distance between the neighboring flanks of signals A and B can then be adjusted to the exact value of an eighth of a cycle (a 45° angle distance).

Figure 16: Calibration using incremental signals

Rev A0.9, Page 18/25

### **Sine/Digital Converter**

The iC-MH8 module integrates a high-resolution sine/digital converter. In the highest output resolution with an interpolation factor of 1024, 4096 edges per rotation are generated and 4096 angular steps can be differentiated. Even in the highest resolution, the absolute position can be calculated in real time at the maximum speed.

This absolute position is used to generate quadrature signals (ABZ) and commutation signals (UVW). The zero point of the quadrature signals and the commutation signals can be set seperately. This enables the commutation at other angles based on the index track Z.

The resolution of the incremental output signals is programmed with CFGRES.

The value of the 12-bit sine-digital converter is available *in full resolution* in the 'Extended SSI-Mode' and *in a resolution according to CFGRES* in the 'SSI-Mode'.

| CFGRES(2: | 0)   | Addr. 0x06; | bit 3:0 |

|-----------|------|-------------|---------|

| 0x0       | 1024 |             |         |

| 0x1       | 512  |             |         |

| 0x2       | 256  |             |         |

| 0x3       | 128  |             |         |

| 0x4       | 64   |             |         |

| 0x5       | 32   |             |         |

| 0x6       | 16   |             |         |

| 0x7       | 8    |             |         |

| 0x8       | 4    |             |         |

| 0x9       | 2    |             |         |

| 0xA       | 1    |             |         |

| Table 15: | Programming | interpolation | factor |

|-----------|-------------|---------------|--------|

|           |             |               |        |

After the resolution is changed, a module reset is triggered internally and the absolute position is recalculated.

| CFGAB(1:0) | Addr. 0x08; bit 1:0  |  |

|------------|----------------------|--|

| 0x0        | A and B not inverted |  |

| 0x1        | B inverted, A normal |  |

| 0x2        | A inverted, B normal |  |

| 0x3        | A and B inverted     |  |

Table 16: Inversion of AB signals

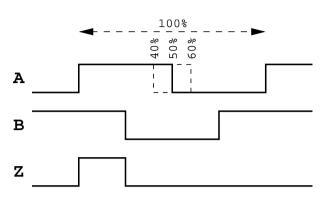

Figure 17: ABZ signals and relative accuracy

The incremental signals can be inverted again independently of the output drivers. As a result, other phase angles of A and B relative to the index pulse Z can be generated. The standard is A and B *high* level for the zero point, i.e. Z is equal to *high*.

Figure 17 shows the position of the incremental signals around the zero point. The relative accuracy of the edges to each other at a resolution setting of 10 bit is better than 10%. This means that, based on a period at A or B, the edge occurs in a window between 40% and 60%.

| CFGHYS(1: | 0)    | Addr. 0x08; | bit 7:6 |

|-----------|-------|-------------|---------|

| 0x0       | 0,17° |             |         |

| 0x1       | 0,35° |             |         |

| 0x2       | 0,7°  |             |         |

| 0x3       | 1,4°  |             |         |

Table 17: Programming angular hysteresis

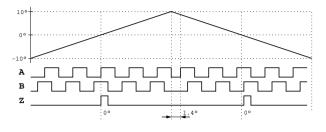

With rotating direction reversal, an angular hysteresis prevents multiple switching of the incremental signals at the reversing point. The angular hysteresis corresponds to a slip which exists between the two rotating directions. However, if a switching point is approached from the same direction, then the edge is always generated at the same position on the output. The following figure shows the generated quadrature signals for a resolution of 360 edges per rotation (interpolation factor 90) and a set angular hysteresis of 1.4°.

Rev A0.9, Page 19/25

At the reversal point at  $+10^{\circ}$ , first the corresponding edge is generated at A. As soon as an angle of  $1.4^{\circ}$ has been exceeded in the other direction in accordance with the hysteresis, the return edge is generated at A again first. This means that all edges are shifted by the same value in the rotating direction.

| CFGZPOS( | 7:0) Addr. 0x07; bit 7:0 |  |

|----------|--------------------------|--|

| 0x0      | 0°                       |  |

| 0x1      | 1,4°                     |  |

| 0x2      | 2,8°                     |  |

|          | 360<br>256 · CFGZPOS     |  |

| 0xFF     | 358,6°                   |  |

Table 18: Programming AB zero position

The position of the index pulse Z can be set in  $1.4^{\circ}$  steps. An 8-bit register is provided for this purpose, which can shift the Z-pulse once over  $360^{\circ}$ .

| CFGMTD(2 | :0) Addr. 0x06; bit 6:4                                        |

|----------|----------------------------------------------------------------|

| 0        | Minimum edge spacing 125 ns at IPO 1024 (max.<br>2 MHz at A)   |

| 1        | Minimum edge spacing 250 ns at IPO 1024                        |

| 2        | Minimum edge spacing 500 ns at IPO 1024 (max.<br>500 kHz at A) |

| 3        | Minimum edge spacing 1 µs at IPO 1024                          |

| 4        | Minimum edge spacing 2 µs at IPO 1024                          |

| 5        | Minimum edge spacing 4 µs at IPO 1024                          |

| 6        | Minimum edge spacing 8 µs at IPO 1024                          |

| 7        | Minimum edge spacing 16 µs at IPO 1024                         |

Table 19: Minimum edge spacing

The CFGMTD register defines the time in which two consecutive position events can be output at the highest resolution. The default is a maximum output frequency of 500 kHz on A. This means that at the highest resolution, speeds of 30,000 rpms can still be correctly shown. In the setting with an edge spacing of 125 ns, the edges can be generated even at the highest revolution and the maximum speed. However, the counter connected to the module must be able to correctly process all edges in this case. The settings with 2  $\mu$ s, and 8  $\mu$ s can be used for slower counters.

It should be noted then, however, that the maximum rotation speed is reduced.

| CFGDIR | Addr. 0x08; bit 5      |

|--------|------------------------|

| 0      | Rotating direction CCW |

| 1      | Rotating direction CW  |

| Table 20: | Rotating | direction | reversal |

|-----------|----------|-----------|----------|

|           | rotating | anoonon   | 10101001 |

The rotating direction can easily be changed with the bit CFGDIR. When the setting is CCW (counterclockwise, CFGDIR = '0') the resulting angular position values will increase when rotation of the magnet is performed as shown in figure 5. To obtain increasing angular position values in the CW (clockwise) direction, CFGDIR then has to be set to '1'.

The internal analoge sine and cosine signal which are available in test mode are not affected by the setting of CFGDIR. They will always appear as shown in figure 5.

| CFGSU | Addr. 0x08; bit 4                        |  |

|-------|------------------------------------------|--|

| 0     | ABZ output "111" during startup          |  |

| 1     | AB instantly counting to actual position |  |

| Table 21: Configuration of our | tput startup |

|--------------------------------|--------------|

|--------------------------------|--------------|

Depending on the application, a counter cannot bear generated pulses while the module is being switched on. When the supply voltage is being connected, first the current position is determined. During this phase, the quadrature outputs are constantly set to "111". In the setting CFGSU = '1', edges are generated at the output until the absolute position is reached. This enables a detection of the absolute position with the incremental interface.

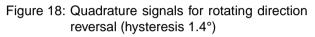

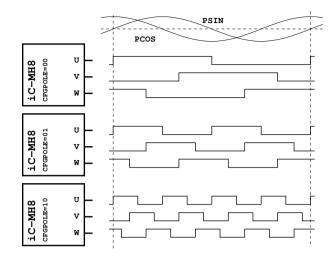

The converter for the generation of the commutation signals can be configured for two, four and eight-pole motors. Three rectangular signals each with a phase shift of 120° are generated. With two-pole commutation, the sequence repeats once per rotation. With a four-pole setting, the commutation sequence is generated twice per rotation. With a eight-pole setting, the commutation sequence is generated four times per rotation.

Figure 19: UVW signals for different settings of CFGPOLE

| CFGPOLE( | 1:0) Addr. 0x8; bit 3,2 |

|----------|-------------------------|

| 00       | 2 pole commutation      |

| 01       | 4 pole commutation      |

| 1-       | 8 pole commutation      |

Table 22: Commutation

The zero position of the commutation, i.e. the rising edge of the track U, can be set as desired over a rotation. Here 256 possible positions are available.

| CFGCOM(7 | :0) Addr. 0x09; bit 7:0 |

|----------|-------------------------|

| 0x00     | 0°                      |

| 0x01     | -1,4°                   |

|          | - <u>360</u> · CFGCOM   |

Table 23: Commutation

Rev A0.9, Page 21/25

### **Output Drivers**

Six RS422-compatible output drivers are available, which can be configured for the incremental signals and commutation signals. The following table on the CFGO register bits provides an overview of the possible settings.

| CFGO(1:0) | Addr. 0x05; bit 5:4                      |  |

|-----------|------------------------------------------|--|

| 00        | Incrementral Diff ABZ (U=NA, V=NB, W=NZ) |  |

| 01        | Incr ABZ + Comm UVW                      |  |

| 10        | Commutation Diff UVW (A=NU, B=NV, Z=NW)  |  |

| 11        | Incr. ABZ + AB4 (U=A4, V=B4, W=0)        |  |

Table 24: Configuration of output drivers

In the differential incremental mode (CFGO = '00', Figure 20), quadrature signals are available on the Pins A, B and Z. The respective inverted quadrature signals are available on the pins U, V and W. As a result, lines can be connected directly to the module. Another configuration of the incremental signals is specified in the section "Sine/Digital Converter".

With CFGO = '01' (Figure 21) the ABZ incremental signals and the UVW commutation signals are available on the six pins. As long as the current angular position is not yet available during the start-up phase, all commutation signals are at the low level.

With CFGO = '10', the third mode (Figure 22) is available for transferring the commutation signals via a differential line. The non-inverted signals are on the pins U, V and W, the inverted signals on A, B and Z.

The ABZ quadrature signals with an adjustable higher resolution and quadrature signals with one period per rotation are available in the fourth mode (Figure 23). Four segments can be differentiated with the pins U and V. This information can be used for an external period counter which counts the number of scanned complete rotations.

Figure 20: ABZ differential incremental signals

Figure 21: ABZ and UVW single ended signals

Figure 22: UVW differential commutation signals

Figure 23: ABZ incremental signals / period counter

Rev A0.9, Page 22/25

The property of the RS422 driver of the connected line can be adjusted in the CFGDR register.

| CFGDR(1:0) | Addr. 0x05; bit 1:0   |

|------------|-----------------------|

| 00         | 10 MHz 4 mA (default) |

| 01         | 10 MHz 60 mA          |

| 10         | 300 kHz 60 mA         |

| 11         | 3 MHz 20 mA           |

Table 25: Driver property

Signals with the highest frequency can be transmitted in the setting CFGDR = '00'. The driver capability is at least 4 mA, however it is not designed for a  $100 \Omega$ line. This mode is ideal for connection to a digital input on the same assembly. With the setting CFGDR = '01' the same transmission speed is available and the driver power is sufficient for the connection of a line over a short distance. Steep edges on the output enable a high transmission rate. A lower slew rate is offered by the setting CFGDR = '10', which is excellent for longer lines in an electromagnetically sensitive environment. Use of the setting CFGDR = '11' is advisable at medium transmission rates with a limited driver capability.

| TRIHL | Addr. 0x05; bit 3:2    |

|-------|------------------------|

| 00    | Push Pull Output Stage |

| 01    | Highside Driver        |

| 10    | Lowside Driver         |

| 11    | Tristate               |

Table 26: Tristate Register

The drivers consist of a push-pull stage in each case with low-side and high-side drivers which can each be activated individually. As a result, open-drain outputs with an external pull-up resistor can also be realized.

### Serial Interface

The serial interface is used to read out the absolute position and to parameterize the module. For a de-

tailed description of the protocol, see separate interface specification.

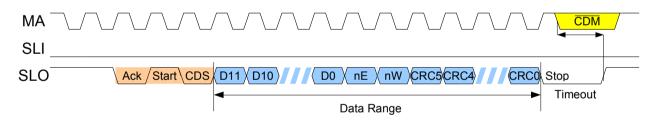

The sensor sends a fixed cycle-start sequence containing the Acknowledge-, Start and Control-Bit followed by the binary 12 bit sensor data. The low-active error bit nE a '0' indicates an error which can be further identified by reading the status register 0x77. The following bit nW is always at '1' state. Following the 6 CRC bits the data of the next sensors, if available, are presented. Otherwise, the master stops generating clock pulse on the MA line an the sensor runs into a timeout, indicating the end of communication.

| Serial Interface<br>Protocol | Mode C              |

|------------------------------|---------------------|

| Cycle start sequence         | Ack/Start/CDS       |

| Lenght of sensor data        | 12 Bit + ERR + WARN |

| CRC Polynom                  | 0b1000011           |

| CRC Mode                     | inverted            |

| Multi Cycle Data             | not available       |

| max. Data Rate               | 10 MHz              |

Table 27: Interface Protocol

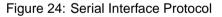

| ENSSI | Addr. 0x05; bit 7 |

|-------|-------------------|

| 0     | Extended SSI-Mode |

| 1     | SSI-Mode          |

Table 28: Activation of SSI mode

forced by applying V(VZAP) = V()ZAP before changing the value of Bit ENSSI to avoid an aborted register communication.

In the SSI mode the absolute position is output with 13 bits according to the SSI standard. (The data is transmitted as Gray code with trailing zeros.)

Figure 25: SSI protocol, data GRAY-coded

The register range 0x00 to 0x0F is equivalent to the settings with which the IC can be parameterized. The settings directly affect the corresponding switching parts. The range 0x10 to 0x1F is read-only and reflects the contents of the integrated zapping diodes. Following programming the data can be verified via these addresses. After the supply voltage is connected, the contents of the zapping diodes are copied to the RAM area 0x00 to 0x0F. Then the settings can be overwritten via the serial interface. Overwriting is not possible if the CFGPROT bit is set.

Errors in the module are signaled via the error message output NERR. This open-drain output signals an error if the output is pulled against VND. If the error condition no longer exists, then the pin is released again after a waiting time of approximately 1 ms. If the integrated pull-up resistor is deactivated with DPU = '1', then an external resistor must be provided. With DPU = '0' it brings the pin up to the high level again.

| DPU | Addr. 0x04; bit 6 |

|-----|-------------------|

| 0   | Pull-up activated |

| 1   | Pull-up deactive  |

Table 29: Activation of NERR pull-up

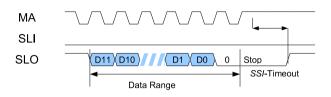

## **OTP Programming**

| CFGPROT | Addr. 0x05; bit 6     |  |

|---------|-----------------------|--|

| 0       | no protection         |  |

| 1       | write/read protection |  |

Table 31: Write/read protection of configuration

Rev A0.9, Page 23/25

With the profile ID, the data format can be requested for the following sensor data cycles in the module. A read operation at address 0x42 results in 0x2C, with is the equivalent to 12-bit single-cycle data.