Rev E1, Page 1/33

### FEATURES

- iC-MHL200 TSSOP20 AEC-Q100 qualified (Grade 1)

- Realtime system for linear speed up to 8 m/s at full resolution

- Absolute position within the magnetic period of 4 mm

- 12-bit interpolation w. 4 096 increments, resolution better 1 μm

- ♦ Automatic signal offset compensation

- Automatic amplitude control for optimum operating point

- Programmable features: interpolation factor, hysteresis, minimum phase distance, zero position and code direction

- Electronic index generation with multi-purpose enable input

- RS422-compatible A/B/Z outputs for encoder quadrature signals with up to 8 MHz edge rate

- UVW commutation signals for EC motor applications

- BiSS/SSI interface for high-speed serial data output (BiSS/SSI) and configuration (BiSS)

- Zener-Zap ROM for non-volatile setup and OEM data

- Signal monitoring: loss of signal, excessive frequency

- ♦ Single 5 V supply

- Extended temperature range of -40 to +125 °C

## APPLICATIONS

- Motion control

- Linear position encoders

- Incremental off-axis rotary encoders

- Brushless motors

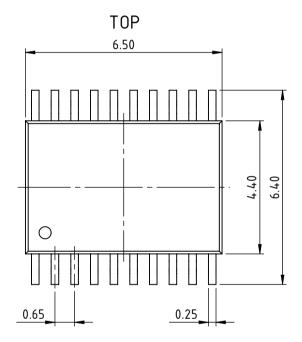

## PACKAGES

TSSOP20 6.4 mm x 6.5 mm x 1 mm RoHS compliant

Rev E1, Page 2/33

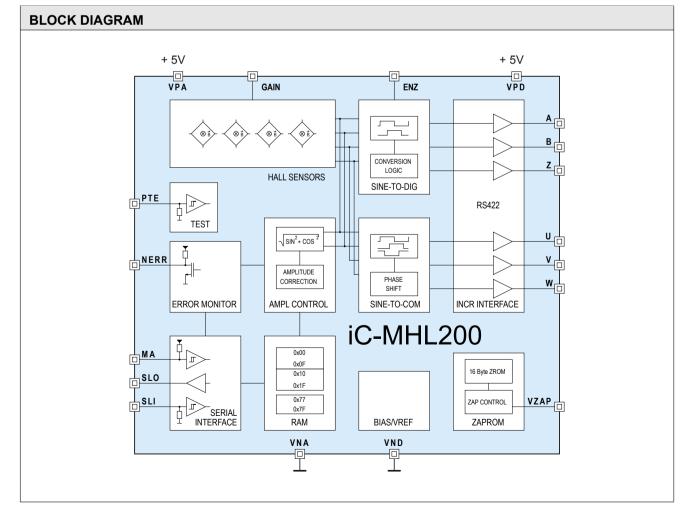

### DESCRIPTION

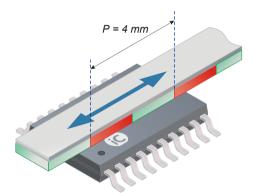

The iC-MHL200 is a magnetic position sensor with integrated Hall sensors for the scanning of magnetic tapes and pole wheels featuring a pole pitch of 2 mm. Moving speeds of up to 8 m/s can be followed even at highest resolution representing  $0.98 \,\mu$ m.

The signal conditioning unit generates constant-amplitude sine and cosine voltages that are used for real-time tracking sine-to-digital angle conversion. The resolution can be programmed up to a maximum of 4 096 increments within one magnetic period of 4 mm.

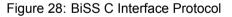

The integrated BiSS interface enables daisy-chain operation of multiple devices with a synchronous position capture at all networked sensors. The device's memory can also be accessed via the bidirectional BiSS C protocol without interfering the readout cycles.

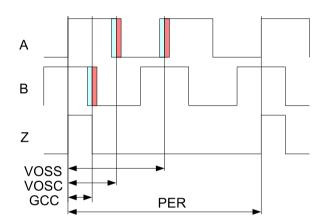

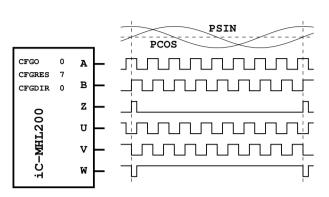

The incremental interface with the pins A, B and Z supplies encoder quadrature signals at an edge rate of up to 8 MHz. Complementary incremental signals are available at the U, V, W outputs. The index position at the Z output is adjustable and can be gated via enable input ENZ.

An additional converter operates for commutation signals UVW. The resolution of the interface depends on the pole pair count of the magnetic target. For instance, with a magnetic target of 10 pole pairs a EC-motor with 10 or 20 pole pairs can be commutated depending on chip setting. The zero point of the commutation signals can be set separately from the quadrature converter. A/B/Z and U/V/W form RS422-compatible outputs and are programmable regarding the output's drive current and slew rate.

A gain-dependent analog signal is available at the GAIN output, which can be used to monitor mechanical alignment of the sensor with respect to the magnetic target.

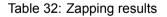

All device parameters can be stored in the internal non-volatile Zener-zapping ROM to allow self-configuration after power on. The required writing algorithm for programming is executed by the IC itself.

Together with the appropriate magnetic scale or pole wheel, the iC-MHL200 provides a single-chip solution for linear and rotary encoders.

**Note:** Parameters defined in the datasheet represent supplier's attentive tests and validations, but by principle - do not imply any warranty or guarantee as to their accuracy, completeness or correctness under all application conditions. In particular, setup conditions, register settings and power-up have to be thoroughly validated by the user within his specific application environment and requirements (system responsibility). The chip's performance in application is impacted by system conditions like the quality of the magnetic target, field strength and stray fields, temperature and mechanical stress, sensor alignment and initial calibration.

Rev E1, Page 3/33

## **PACKAGING INFORMATION TSSOP20**

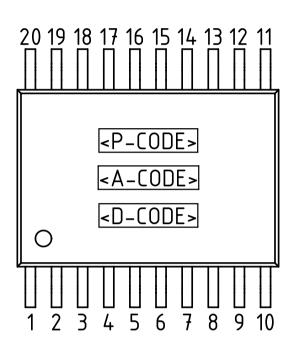

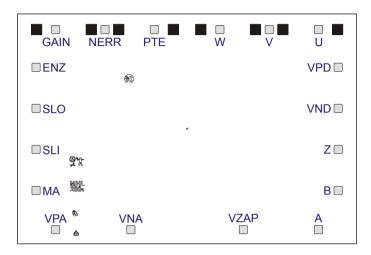

#### **PIN CONFIGURATION TSSOP20**

#### **PIN FUNCTIONS** No. Name Function

| SLI <sup>1)</sup> | BiSS Interface, Data Input                                                                                                                            |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| MA                | BiSS Interface, Clock Input                                                                                                                           |

| VPA               | +5 V Supply Voltage (analog)                                                                                                                          |

| VNA               | Ground (analog)                                                                                                                                       |

| nc                | not connected                                                                                                                                         |

| nc                | not connected                                                                                                                                         |

| VZAP              | Zener Zapping Programming Voltage                                                                                                                     |

| А                 | Incremental Output A (+ NU)                                                                                                                           |

| В                 | Incremental Output B (+ NV)                                                                                                                           |

| Z                 | Index Output Z (+ NW)                                                                                                                                 |

| VND               | Ground (digital)                                                                                                                                      |

| VPD               | +5 V Supply Voltage (digital)                                                                                                                         |

| U                 | Commutation U (+NA)                                                                                                                                   |

| V                 | Commutation V (+NB)                                                                                                                                   |

| W                 | Commutation W (+NZ)                                                                                                                                   |

| PTE <sup>1)</sup> | Test Enable Pin                                                                                                                                       |

| NERR              | Error Output (active low)                                                                                                                             |

| GAIN              | Gain-Signal                                                                                                                                           |

| ENZ               | Enable Index Z                                                                                                                                        |

| SLO               | BiSS Interface, Data Output                                                                                                                           |

|                   | MA<br>VPA<br>VNA<br>nc<br>nc<br>VZAP<br>A<br>B<br>Z<br>VND<br>VPD<br>U<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>PTE <sup>1)</sup><br>NERR<br>GAIN<br>ENZ |

Orientation of the logo (**©** MHL CODE ...) is subject to alteration. IC top marking: <P-CODE> = product code, <A-CODE> = assembly code (subject to changes), <D-CODE> = date code (subject to changes); <sup>1)</sup> If not used, the pin must be connect to VNA, VND.

Rev E1, Page 4/33

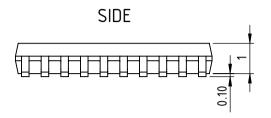

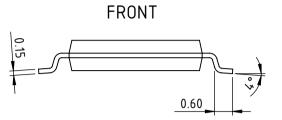

## PACKAGE DIMENSIONS

All dimensions given in mm. Tolerances of form and position according to JEDEC M0–153

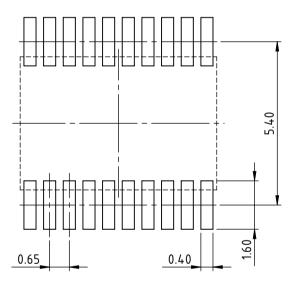

## RECOMMENDED PCB-FOOTPRINT

dra\_tssop20-1\_pack\_1, 8:1

Rev E1, Page 5/33

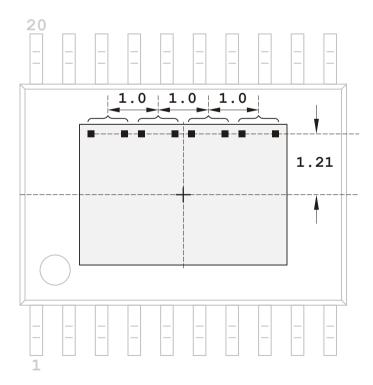

## **CHIP-LAYOUT**

### Chip size: 4.13 mm x 2.80 mm

Figure 1: MHL200 Chip with contact pads shown in grey, Hall sensors shown in black

### HALL SENSOR LOCATIONS

## All dimensions in mm

Figure 2: Hall sensor array of four sensor pairs spaced 1mm apart.

Rev E1, Page 6/33

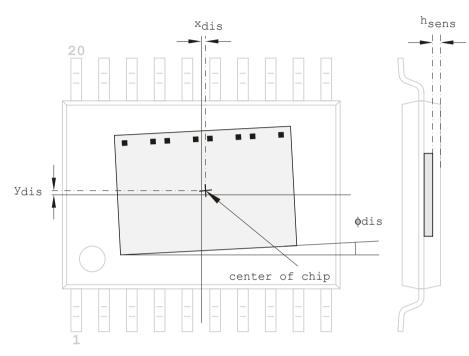

## CHIP LOCATION WITHIN TSSOP20 PACKAGE

Figure 3: Definition of lateral and rotational displacements

Rev E1, Page 7/33

## **ABSOLUTE MAXIMUM RATINGS**

Beyond these values damage may occur; device operation is not guaranteed.

| Item | Symbol  | Parameter                                                | Conditions                        |      |      | Unit |

|------|---------|----------------------------------------------------------|-----------------------------------|------|------|------|

| No.  | -       |                                                          |                                   | Min. | Max. |      |

| G001 | V()     | Voltage at VPA, VPD                                      |                                   | -0.3 | 6    | V    |

| G002 | V(VZAP) | Zapping Voltage                                          |                                   | -0.3 | 8    | V    |

| G003 | V()     | Voltages at A, B, Z, U, V, W, MA, SLO,<br>SLI, NERR, PTE |                                   | -0.3 | 6    | V    |

| G004 | I()     | Current in VPA                                           |                                   | -10  | 20   | mA   |

| G005 | I()     | Current in VPD                                           |                                   | -20  | 200  | mA   |

| G006 | I()     | Current in A, B, Z, U, V, W                              |                                   | -100 | 100  | mA   |

| G007 | I()     | Current in MA, SLO, SLI, NERR, PTE                       |                                   | -10  | 10   | mA   |

| G008 | Vd()    | ESD-voltage, all Pins                                    | CDM (JEDEC Standard No. 22-C101F) |      | 500  | V    |

| G009 | Ts      | Storage Temperature                                      |                                   | -40  | 150  | °C   |

| G010 | Tj      | Junction Temperature                                     |                                   | -40  | 150  | °C   |

### THERMAL DATA

#### Operating conditions: VPA, VPD = $5V \pm 10\%$

| Item | Symbol | Parameter                       | Conditions             |      |      |      | Unit |

|------|--------|---------------------------------|------------------------|------|------|------|------|

| No.  |        |                                 |                        | Min. | Тур. | Max. |      |

| T01  | Та     | Ambient Temperature             |                        | -40  |      | 125  | °C   |

| T02  | Rthja  | Thermal Resistance Chip/Ambient | package mounted on PCB |      | 100  |      | K/W  |

Rev E1, Page 8/33

## **ELECTRICAL CHARACTERISTICS**

Operating conditions: VPA, VPD = 5 V ±10 %, Tj = -40...125 °C, IBM adjusted to 200  $\mu A$  , unless otherwise noted

| ltem<br>No. | Symbol         | Parameter                                             | Conditions                                                | Min.         | Тур. | Max.         | Unit           |

|-------------|----------------|-------------------------------------------------------|-----------------------------------------------------------|--------------|------|--------------|----------------|

| Gener       | al             | -                                                     | · · · · · · · · · · · · · · · · · · ·                     |              |      |              | u              |

| 001         | V(VPA,<br>VPD) | Permissible Supply Voltage                            |                                                           | 4.5          |      | 5.5          | V              |

| 002         | I(VPA)         | Supply Current in VPA                                 |                                                           |              | 5    | 8            | mA             |

| 003         | I(VPD)         | Supply Current in VPD                                 | PRM = 0, without load                                     |              | 10   | 18           | mA             |

| 004         | I(VPD)         | Supply Current in VPD                                 | PRM = 1, without load                                     |              | 4    | 8            | mA             |

| 005         | Vc(hi)         | Clamp-Voltage hi at MA, SLI,<br>SLO, PTE, NERR        | Vc()hi = V() — VPD, I() = 1 mA                            | 0.4          |      | 1.5          | V              |

| 006         | Vc(lo)         | Clamp-Voltage lo                                      | I() = -1 mA                                               | -1.5         |      | -0.3         | V              |

| Hall S      | ensors and     | Signal Conditioning                                   |                                                           |              |      |              |                |

| 101         | Hext           | Operating Magnetic Field<br>Strength                  | at chip surface                                           | 20           |      | 100          | kA/m           |

| 102         | fmag           | Operating Magnetic Field<br>Frequency<br>Linear Speed | with resolution set to 4 096, MTD set to 125 ns           |              |      | 2<br>8       | kHz<br>m/s     |

| 105         | xdis, ydis     | Displacement Chip to Package                          | TSSOP package, see Figure 3                               | -0.2         |      | 0.2          | mm             |

| 106         | $\phi$ dis     | Angular Alignment of Chip vs.<br>Package              | TSSOP package, see Figure 3                               | -3           |      | +3           | Deg            |

| 107         | hsens          |                                                       | TSSOP package, see Figure 3                               |              | 0.4  |              | mm             |

| 108         | Vos            | Trimming Range of Output Offset Voltage               | VOSS or VOSC = 0x7F                                       |              |      | -55          | mV             |

| 109         | Vos            | Trimming Range of Output Offset Voltage               | VOSS or VOSC = 0x3F                                       | 55           |      |              | mV             |

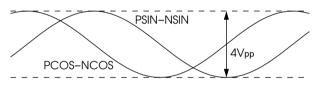

| 110         | Vopt           | Optimal Differential Output Volt-<br>age              | Vopt = Vpp(PSIN) – Vpp(NSIN), ENAC = 0, see<br>Figure 11  |              | 4    |              | Vpp            |

| Ampli       | tude Contro    | ol                                                    |                                                           |              |      |              |                |

| 201         | Vampl          | Differential Output Amplitude                         | Vampl = Vpp(PSIN) – Vpp(NSIN), ENAC = 1,<br>see Figure 11 | 3.2          |      | 4.8          | Vpp            |

| 202         | Vratio         | Amplitude Ratio                                       | Vratio = Vpp(PSIN) / Vpp(PCOS)                            | 1.09         |      |              |                |

| 203         | Vratio         | Amplitude Ratio                                       | Vratio = Vpp(PSIN) / Vpp(PCOS)                            |              |      | 0.92         |                |

| 204         | tampl          | Settling Time of Amplitude Con-<br>trol               | ±10%                                                      |              |      | 300          | μs             |

| 205         | Vae()lo        | Amplitude Error Threshold for<br>MINERR               | Vpp(PSIN) – Vpp(NSIN)                                     | 1.0          |      | 2.8          | Vpp            |

| 206         | Vae()hi        | Amplitude Error Threshold for<br>MAXERR               | Vpp(PSIN) – Vpp(NSIN)                                     | 4.8          |      | 5.8          | Vpp            |

| Bandg       | gap Referen    | ice                                                   |                                                           |              |      |              |                |

| 401         | Vbg            | Bandgap Reference Voltage                             |                                                           | 1.18         | 1.25 | 1.32         | V              |

| 402         | Vref           | Reference Voltage                                     |                                                           | 45           | 50   | 55           | %VPA           |

| 403         | libm           | Bias Current                                          | CIBM = 0x0<br>CIBM = 0xF<br>Bias Current adjusted         | -370<br>-220 | -200 | -100<br>-180 | μΑ<br>μΑ<br>μΑ |

| 404         | VPDon          | Turn-on Threshold VPD, System                         | V(VPD) – V(VND), increasing voltage                       | 3.65         | 4.0  | 4.3          | V              |

| 405         | VPDoff         | Turn-off Threshold VPD, System reset                  | V(VPD) – V(VND), decreasing voltage                       | 3            | 3.5  | 3.8          | V              |

| 406         | VPDhys         | Hysteresis System on/reset                            |                                                           | 0.3          |      |              | V              |

| 407         | Vosr           | Reference Voltage Offset Com-<br>pensation            |                                                           | 475          | 500  | 525          | mV             |

Rev E1, Page 9/33

## **ELECTRICAL CHARACTERISTICS**

Operating conditions: VPA, VPD = 5 V ±10 %, Tj = -40...125 °C, IBM adjusted to 200  $\mu A$  , unless otherwise noted

| ltem<br>No. | Symbol       | Parameter                                             | Conditions                                                                                  | Min.  | Тур.       | Max. | Unit       |

|-------------|--------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------|-------|------------|------|------------|

| Clock       | Generation   | 1                                                     | 1                                                                                           | 0     |            |      |            |

| 501         | f()sys       | System Clock                                          | bias current adjusted                                                                       | 0.85  | 1.0        | 1.2  | MHz        |

| 502         | f()sdc       | Sine-to-Digital Converter Clock                       | bias current adjusted                                                                       | 13.5  | 16         | 18   | MHz        |

| Sine-te     | o-Digital Co | nverter                                               |                                                                                             |       |            |      |            |

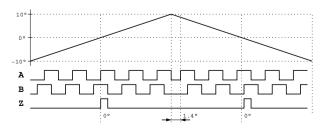

| 602         | AAabs        | Absolute Angular Accuracy                             | Vpp() = 4 V, adjusted                                                                       | -0.35 |            | 0.35 | Deg        |

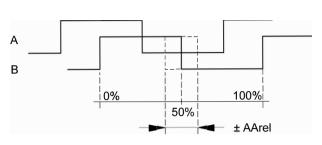

| 603         | AArel        | Relative Angular Accuracy                             | with reference to one output period at A, B, at resolution 512 (CFGRES = 0x7F), see Fig. 22 | -15   | ±10        | 15   | %          |

| 604         | f()ab        | Output Frequency at A, B                              | CFGMTD = 0<br>CFGMTD = 1                                                                    |       | 0.5<br>2.0 |      | MHz<br>MHz |

| 605         | REScom       | Resolution of Commutation Con-<br>verter              |                                                                                             |       | 1.875      |      | Deg        |

| 606         | AAabs        | Absolute Angular Accuracy of<br>Commutation Converter |                                                                                             | -0.5  |            | 0.5  | Deg        |

| BiSS I      | nterface, Di | gital Output SLO, Digital Inputs I                    | MA, SLI                                                                                     |       |            |      |            |

| 701         | Vs(SLO)hi    | Saturation Voltage hi                                 | V(SLO) = V(VPD) - V(),<br>I(SLO) = 4 mA                                                     |       |            | 0.4  | V          |

| 702         | Vs(SLO)lo    | Saturation Voltage lo                                 | I(SLO) = 4 mA to VND                                                                        |       |            | 0.4  | V          |

| 703         | lsc(SLO)hi   | Short-Circuit Current hi                              | V(SLO) = V(VND), 25 °C                                                                      | -90   | -50        |      | mA         |

| 704         | lsc(SLO)lo   | Short-Circuit Current lo                              | V(SLO) = V(VPD), 25 °C                                                                      |       | 50         | 80   | mA         |

| 705         | tr(SLO)      | Rise Time SLO                                         | CL = 50 pF                                                                                  |       |            | 60   | ns         |

| 706         | tf(SLO)      | Fall Time SLO                                         | CL = 50 pF                                                                                  |       |            | 60   | ns         |

| 707         | Vt()hi       | Threshold Voltage hi: MA, SLI                         |                                                                                             |       |            | 2    | V          |

| 708         | Vt()lo       | Threshold Voltage Io: MA, SLI                         |                                                                                             | 0.8   |            |      | V          |

| 709         | Vt()hys      | Threshold Hysteresis: MA, SLI                         |                                                                                             | 140   | 250        |      | mV         |

| 710         | Ipd(SLI)     | Pull-Down Current: SLI                                | V()= 1 VVPD                                                                                 | 6     | 30         | 65   | μA         |

| 711         | Ipu(MA)      | Pull-Up Current MA                                    |                                                                                             | -60   | -30        | -6   | μA         |

|             | f()MA        | Permissible Frequency at MA                           |                                                                                             |       |            | 10   | MHz        |

| Zappir      | -            | I Test VZAP, PTE                                      | 1                                                                                           |       |            |      |            |

| 801         | Vt()hi       | Threshold Voltage hi VZAP, PTE                        | with reference to VND                                                                       |       |            | 2    | V          |

| 802         | Vt()lo       | Threshold Voltage lo VZAP, PTE                        | with reference to VND                                                                       | 0.8   |            |      | V          |

| 803         | Vt()hys      | Hysteresis                                            | Vt()hys = Vt()hi – Vt()lo                                                                   | 140   | 250        |      | mV         |

| 804         | Vt()nozap    | Threshold Voltage Nozap VZAP                          | $V() = V(VZAP) - V(VPD), V(VPD) = 5 V \pm 5 \%,$<br>at chip temperature 27 °C               | 0.7   |            |      | V          |

| 805         | Vt()zap      | Threshold Voltage Zap VZAP                            | $V() = V(VZAP) - V(VPD), V(VPD) = 5 V \pm 5 \%,$<br>at chip temperature 27 °C               |       |            | 1.2  | V          |

| 806         | V()zap       | Zapping Voltage                                       | PROG = 1                                                                                    | 6.9   | 7.0        | 7.1  | V          |

| 807         | V()zpd       | Diode voltage, Zapped                                 | for iC-Haus chip test only                                                                  |       |            | 2    | V          |

| 808         | V()uzpd      | Diode Voltage, Unzapped                               | for iC-Haus chip test only                                                                  | 3     |            |      | V          |

|             |              | Pull-down Resistor at VZAP                            | V()=0VV(VPD)                                                                                | 30    |            | 55   | kΩ         |

|             | Ipd(PTE)     | Pull-Down Current PTE                                 | V() = 1 VVPD                                                                                | 6     | 30         | 65   | μA         |

|             | Monitor NE   | ·                                                     | 1                                                                                           | n     | 1          |      |            |

| 901         | Vt()hi       | Input Threshold Voltage hi                            | with reference to VND                                                                       |       |            | 2    | V          |

| 902         | Vs()lo       | Saturation Voltage lo                                 | I() = 4 mA , with reference to VND                                                          |       |            | 0.4  | V          |

| 903         | Vt()lo       | Input Threshold Voltage lo                            | with reference to VND                                                                       | 0.8   |            |      | V          |

| 904         | Vt()hys      | Input Hysteresis                                      | Vt()hys = Vt()hi - Vt()lo                                                                   | 140   | 250        |      | mV         |

| 905         | Ipu(NERR)    | Pull-up Current                                       | V(NERR) = 0VPD - 1 V                                                                        | -800  | -300       | -80  | μA         |

| 906         | lsc()lo      | Short-Circuit Current NERR                            | V(NERR) = V(VPD), 25 °C                                                                     |       | 50         | 80   | mA         |

| 907         | tf(NERR)     | Decay Time NERR                                       | CL = 50 pF                                                                                  |       |            | 60   | ns         |

Rev E1, Page 10/33

## **ELECTRICAL CHARACTERISTICS**

Operating conditions: VPA, VPD = 5 V  $\pm$ 10 %, Tj = -40...125 °C, IBM adjusted to 200  $\mu$ A , unless otherwise noted

| ltem<br>No. | Symbol       | Parameter                                   | Conditions                                                                                                                                           | Min.                       | Тур. | Max.                     | Unit                 |

|-------------|--------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|--------------------------|----------------------|

| Line [      | Driver Outp  | uts A, B, Z, U, V, W                        |                                                                                                                                                      |                            |      |                          | I                    |

| P01         | Vs()hi       | Saturation Voltage hi                       | Vs() = VPD - V();<br>CFGDR(1:0) = 00, I() = -4 mA<br>CFGDR(1:0) = 01, I() = -50 mA<br>CFGDR(1:0) = 10, I() = -50 mA<br>CFGDR(1:0) = 11, I() = -20 mA |                            |      | 200<br>700<br>700<br>400 | mV<br>mV<br>mV<br>mV |

| P02         | Vs()lo       | Saturation Voltage lo                       | CFGDR(1:0) = 00, I() = -4 mA<br>CFGDR(1:0) = 01, I() = -50 mA<br>CFGDR(1:0) = 10, I() = -50 mA<br>CFGDR(1:0) = 11, I() = -20 mA                      |                            |      | 200<br>700<br>700<br>400 | mV<br>mV<br>mV<br>mV |

| P03         | lsc()hi      | Short-Circuit Current hi                    | V() = 0 V;<br>CFGDR(1:0) = 00<br>CFGDR(1:0) = 01<br>CFGDR(1:0) = 10<br>CFGDR(1:0) = 11                                                               | -12<br>-125<br>-125<br>-60 |      | -4<br>-50<br>-50<br>-20  | mA<br>mA<br>mA<br>mA |

| P04         | lsc()lo      | Short-Circuit Current lo                    | V() = VPD;<br>CFGDR(1:0) = 00<br>CFGDR(1:0) = 01<br>CFGDR(1:0) = 10<br>CFGDR(1:0) = 11                                                               | 4<br>50<br>50<br>20        |      | 12<br>125<br>125<br>60   | mA<br>mA<br>mA<br>mA |

| P05         | llk()tri     | Leakage Current Tristate                    | TRIHL(1:0) = 11                                                                                                                                      | -100                       |      | 100                      | μA                   |

| P06         | tr()         | Rise-Time lo to hi at Q                     | RL = 100 Ω to VND;<br>CFGDR(1:0) = 00<br>CFGDR(1:0) = 01<br>CFGDR(1:0) = 10<br>CFGDR(1:0) = 11                                                       | 5<br>5<br>50<br>5          |      | 20<br>20<br>350<br>40    | ns<br>ns<br>ns<br>ns |

| P07         | tf()         | Fall-Time hi to lo at Q                     | RL = $100 \Omega$ to VND;<br>CFGDR(1:0) = 00<br>CFGDR(1:0) = 01<br>CFGDR(1:0) = 10<br>CFGDR(1:0) = 11                                                | 5<br>5<br>50<br>5          |      | 20<br>20<br>350<br>40    | ns<br>ns<br>ns<br>ns |

| Outpu       | ut Monitor ( | GAIN                                        |                                                                                                                                                      |                            |      |                          | 1                    |

| Q01         | RES()        | Digital-to-Analog Converter Reso-<br>lution | -                                                                                                                                                    |                            | 8    |                          | bit                  |

| Q02         | lload()      | Permissible Output Current                  |                                                                                                                                                      | -1                         |      | 1                        | mA                   |

| Q03         | dV0()hi      | Output Voltage hi, Rail-to-Rail             | dV0()hi = V(VPA) - V(GAIN); I() = -1 mA<br>ENAC = 0; GAINF = 0x3E                                                                                    |                            |      | 250                      | mV                   |

| Q04         | dV0()lo      | Output Voltage lo, Rail-to-Rail             | l() = 1 mA<br>ENAC = 0; GAINF = 0x02                                                                                                                 |                            |      | 250                      | mV                   |

| Q05         | llk()        | Leakage Current                             | V(GAIN) = 0VPA, CFGTRIG = 1                                                                                                                          | -5                         |      | 5                        | μA                   |

| Q06         | SR()hi       | Slew Rate hi                                | V(GAIN): 20% $ ightarrow$ 80% of range                                                                                                               | 2                          |      |                          | V/µs                 |

| Q07         | SR()lo       | Slew Rate lo                                | V(GAIN): 80% $ ightarrow$ 20% of range                                                                                                               | 2                          |      |                          | V/µs                 |

| Index       | Gating Inp   | ut ENZ                                      |                                                                                                                                                      |                            |      |                          |                      |

| R01         | Vt()hi       | Threshold Voltage hi ENZ                    |                                                                                                                                                      |                            |      | 2                        | V                    |

| R02         | Vt()lo       | Threshold Voltage Io ENZ                    |                                                                                                                                                      | 0.8                        |      |                          | V                    |

| R03         | Vt()hys      | Threshold Hysteresis ENZ                    |                                                                                                                                                      | 100                        | 250  |                          | mV                   |

| R04         | Ipd(ENZ)     | Pull-down Current 30 µA ENZ                 | V()= 1 VV(VPD)                                                                                                                                       | 6                          | 30   | 65                       | μA                   |

Rev E1, Page 11/33

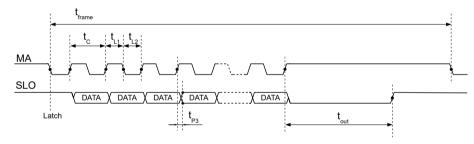

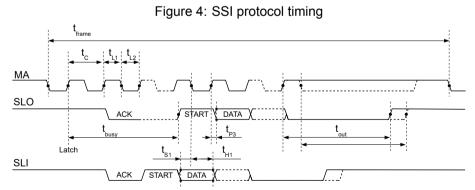

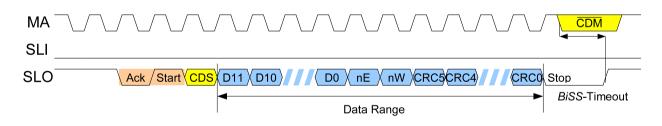

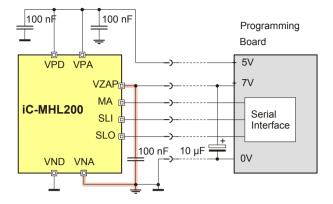

## **OPERATING REQUIREMENTS: Serial Interface**

Operating conditions: VPA, VPD = 5 V  $\pm$ 10 %, Ta = -40...125 °C, IBM calibrated to 200  $\mu$ A; Logic levels referenced to VND: Io = 0...0.45 V, hi = 2.4 V...VPD

| ltem  | Symbol             | Parameter                                            | Conditions                                          |      |                     | Unit |

|-------|--------------------|------------------------------------------------------|-----------------------------------------------------|------|---------------------|------|

| No.   |                    |                                                      |                                                     | Min. | Max.                |      |

| SSI P | rotocol (EN        | ISSI = 1)                                            |                                                     |      |                     |      |

| 1001  | t <sub>C</sub>     | Permissible Clock Period                             | t <sub>out</sub> determined by table 29 on page 28. | 250  | 2x t <sub>out</sub> | ns   |

| 1002  | t <sub>L1</sub>    | Clock Signal Hi-Level Duration                       |                                                     | 25   | t <sub>out</sub>    | ns   |

| 1003  | t <sub>L2</sub>    | Clock Signal Lo-Level Duration                       |                                                     | 25   | t <sub>out</sub>    | ns   |

| 1004  | t <sub>P3</sub>    | Propagation Delay                                    |                                                     | 10   | 50                  | ns   |

| 1005  | t <sub>frame</sub> | Permissible Frame Repetition                         |                                                     | *)   | indefinite          | ns   |

| BiSS  | C Protocol         | (ENSSI = 0)                                          |                                                     |      |                     |      |

| 1006  | t <sub>C</sub>     | Permissible Clock Period                             | t <sub>out</sub> determined by table 29 on page 28. | 100  | 2x t <sub>out</sub> | ns   |

| 1007  | t <sub>L1</sub>    | Clock Signal Hi-Level Duration                       |                                                     | 50   | t <sub>out</sub>    | ns   |

| 1008  | t <sub>L2</sub>    | Clock Signal Lo-Level Duration                       |                                                     | 50   | t <sub>out</sub>    | ns   |

| 1009  | t <sub>busy</sub>  | Data Output Delay                                    | For SLI = 0, i.e. no device in chain                | 2    | 2 t <sub>C</sub>    |      |

| 1011  | t <sub>P3</sub>    | Propagation Delay                                    |                                                     | 10   | 50                  | ns   |

| 1012  | t <sub>out</sub>   | Slave Timeout                                        | t <sub>out</sub> determined by table 29 on page 28. | 2    | 16                  | μs   |

| 1013  | t <sub>S1</sub>    | Setup Time: SLI stable before MA hi $\rightarrow$ lo |                                                     | 25   |                     | ns   |

| 1014  | t <sub>H1</sub>    | Hold Time: SLI stable after MA hi $\rightarrow$ lo   |                                                     | 10   |                     | ns   |

| 1015  | t <sub>frame</sub> | Permissible Frame Repetition                         |                                                     | *)   | indefinite          |      |

Note: \* Allow to elapse.

Figure 5: BiSS protocol timing

Rev E1, Page 12/33

## **REGISTER MAP**

| OVERV    | IEW               |              |                |                   |              |          |                |         |

|----------|-------------------|--------------|----------------|-------------------|--------------|----------|----------------|---------|

| Addr     | Bit 7             | Bit 6        | Bit 5          | Bit 4             | Bit 3        | Bit 2    | Bit 1          | Bit 0   |

| Hall Sig | nal Condition     | ing          |                |                   |              |          |                |         |

| 0x00 z   | GAIN              | G(1:0)       |                |                   | GAIN         | F(5:0)   |                |         |

| 0x01 z   | ENAC              |              |                |                   | GCC(6:0)     |          |                |         |

| 0x02 z   | 1*                |              |                |                   | VOSS(6:0)    |          |                |         |

| 0x03 z   | PRM               |              |                |                   | VOSC(6:0)    |          |                |         |

| 0x04 z   | HCLH              | DPU          | res.           | CFGTOB            |              | CIBM     | (3:0)*         |         |

| RS422 D  | Driver            |              |                |                   |              |          |                |         |

| 0x05 z   | ENSSI             | CFGPROT      | CFG            | D(1:0)            | TRIH         | L(1:0)   | CFGD           | PR(1:0) |

| Sine-to- | Digital Conve     | rter         |                |                   |              |          |                |         |

| 0x06 z   |                   |              |                | CFGRE             |              |          |                |         |

| 0x07 z   |                   |              |                | CFGZP             |              |          |                |         |

| 0x08 z   | CFGH              | YS(1:0)      | CFGDIR         | CFGMTD            | CFGSU        | CFGPOLE  | CFGA           | B(1:0)  |

| 0x09 z   |                   |              |                | CFGCC             |              |          |                |         |

| 0x0A z   |                   | OE           | MA             |                   | CFGTRIG      | CFGZ180  | CFGENZ         | CFGMTD2 |

| 0x0B z   |                   |              |                | OE                |              |          |                |         |

| 0x0C z   |                   |              |                | OE                |              |          |                |         |

| 0x0D     |                   |              |                | OEM               | RAM          |          |                |         |

| Test Set | tings             |              |                |                   |              |          |                |         |

| 0x0E p   | <b>ENULO</b> 2    | 0            | 0              | TEST              |              |          | 0              | 5500745 |

| 0x0F p   | ENHC <sup>2</sup> | 0            | 0              | 0                 | 0            | 0        | 0              | PROGZAP |

|          | des (read onl     | y)           |                | - · · · ·         |              |          |                |         |

| 0x10     |                   |              | ZAP diodes     | s for addresses ( | IX000X0C and | 0x7D0x7F |                |         |

| 0x1F     |                   |              |                |                   |              |          |                |         |

| Not Use  | d                 |              |                |                   |              |          |                |         |

| 0x20     |                   |              |                | 'invalid ad       | dresses'     |          |                |         |

| <br>0x41 |                   |              |                |                   |              |          |                |         |

|          | dentification (   | read only)   |                |                   |              |          |                |         |

| 0x42     |                   |              |                | Profile           | - 0x2C       |          |                |         |

| 0x43     |                   | Profile      | e - 0x0        |                   |              | DLEN     | <b>I</b> (3:0) |         |

| Not Use  | d                 |              |                |                   |              |          |                |         |

| 0x44     |                   |              |                | 'invalid ad       | dresses'     |          |                |         |

| <br>0x75 |                   |              |                |                   |              |          |                |         |

|          | lessages (rea     | d only: mess | ages will be s | et back durin     | a readina)   |          |                |         |

| 0x76     |                   |              |                | GA                | <b>e</b>     |          |                |         |

| 0x77     | PROGERR           | ERRSDATA     | ERRAMIN        | ERRAMAX           | ERREXT       | res.     | res.           | PROGOK  |

<sup>&</sup>lt;sup>2</sup> Regarding chip release 2, please refer to the design review on page 31.

Haus

| EW             |              |                |                                                                                                  |                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|--------------|----------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7          | Bit 6        | Bit 5          | Bit 4                                                                                            | Bit 3                                                                                                                                                                      | Bit 2                                                                                                                                                                                                                                                                                                           | Bit 1                                                                                                                                | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                |

| ntification (0 | x78 bis 0x7B | read-only)     |                                                                                                  |                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |              |                | BiSS Device I                                                                                    | D - 0x4D ('M')                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |              |                | BiSS Device                                                                                      | D - 0x48 ('H')                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |              | Bi             | SS Device ID R                                                                                   | evision - 0x4C ('                                                                                                                                                          | L')                                                                                                                                                                                                                                                                                                             |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |              | BiSS Device ID | Revision - 0x33                                                                                  | 6 (chip: iC-MHL2                                                                                                                                                           | 00, revision: 3)                                                                                                                                                                                                                                                                                                |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |              |                | -                                                                                                |                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                      | CFGTOS                                                                                                                                                                                                                                                                                                                                                                                                               |

|                |              | BiSS [         | Device ID Manufa                                                                                 | acturer Revision                                                                                                                                                           | - 0x00                                                                                                                                                                                                                                                                                                          |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |              | Bi             | SS Device Man                                                                                    | ufacturer ID - 0x                                                                                                                                                          | 00                                                                                                                                                                                                                                                                                                              |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |              | Bi             | SS Device Man                                                                                    | ufacturer ID - 0x                                                                                                                                                          | 00                                                                                                                                                                                                                                                                                                              |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |              | Bit 7 Bit 6    | Bit 7 Bit 6 Bit 5  ntification (0x78 bis 0x7B read-only) Bi BiSS Device IC BiSS Device IC BiSS I | Bit 7 Bit 6 Bit 5 Bit 4<br>ntification (0x78 bis 0x7B read-only)<br>BiSS Device I<br>BiSS Device ID Revision - 0x33<br>-<br>BiSS Device ID Manufa<br>BiSS Device ID Manufa | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3<br>ntification (0x78 bis 0x7B read-only)<br>BiSS Device ID - 0x4D ('M')<br>BiSS Device ID - 0x48 ('H')<br>BiSS Device ID Revision - 0x4C ('<br>BiSS Device ID Revision - 0x33 (chip: iC-MHL2<br>-<br>BiSS Device ID Manufacturer Revision<br>BiSS Device ID Manufacturer Revision | Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2       Intification (0x78 bis 0x7B read-only)     BiSS Device ID - 0x4D ('M') | Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Intification (0x78 bis 0x7B read-only)BiSS Device ID - 0x4D ('M')BiSS Device ID - 0x4D ('M')BiSS Device ID - 0x48 ('H')BiSS Device ID Revision - 0x48 ('H')BiSS Device ID Revision - 0x4C ('L')BiSS Device ID Revision - 0x4C ('L')BiSS Device ID Revision - 0x33 (chip: iC-MHL200, revision: 3)-BiSS Device ID Manufacturer Revision - 0x00BiSS Device ID Manufacturer ID - 0x00 |

z: Register value programmable by zapping

\*: Register value pre-programmed by iC-Haus

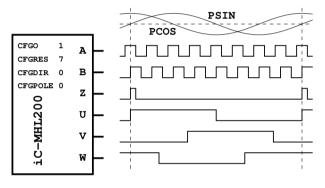

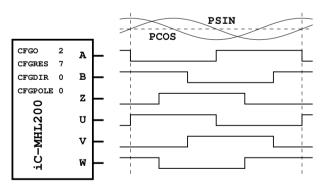

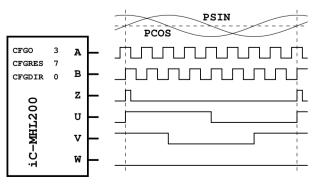

No. of poles for commutation signals

Configuration of incremental output

Zero point for commutation

p: Register value write protected; can only be changed while V(VZAP)> Vt()hi

OEM data

Table 1: Register layout

CFGPOLE:

CFGCOM:

CFGAB:

OEMA:

| Hall Signal Conditioning |  | Page 16 |

|--------------------------|--|---------|

|--------------------------|--|---------|

| GAING:<br>GAINF:<br>GCC:<br>ENAC:<br>VOSS:<br>VOSC:<br>PRM:<br>CIENM: | Hall signal amplification range<br>Hall signal amplification<br>Amplification calibration cosine<br>Activation of amplitude control<br>Offset calibration sine<br>Offset calibration cosine<br>Energy-saving mode |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRM:                                                                  | Energy-saving mode                                                                                                                                                                                                |

| CIBM:                                                                 | Calibration of bias current                                                                                                                                                                                       |

| DPU:                                                                  | Deactivation of NERR pull-up                                                                                                                                                                                      |

| HCLH:                                                                 | Activation of high Hall clock pulse                                                                                                                                                                               |

| CFGTOB:                                                               | Permanent program. BiSS timeout                                                                                                                                                                                   |

|--|

| TEST:    | Test mode                         |

|----------|-----------------------------------|

| PROGZAP: | Activation of programming routine |

| GCC:<br>ENAC:<br>VOSS:<br>VOSC:<br>PRM:<br>CIBM:<br>DPU:<br>HCLH:<br>CFGTOB: | Amplification calibration cosine<br>Activation of amplitude control<br>Offset calibration sine<br>Offset calibration cosine<br>Energy-saving mode<br>Calibration of bias current<br>Deactivation of NERR pull-up<br>Activation of high Hall clock pulse<br>Permanent program. BiSS timeout | CFGTRIG:<br>CFGZ180:<br>CFGENZ:<br>CFGMTD2:<br>OEMB:<br>OEMC:<br>OEMRAM: | Tristate GAIN and output<br>90 $^{\circ} \rightarrow$ 180 $^{\circ}$ zero signal<br>(synchronous with B)<br>Inverting enable Z<br>Frequency at AB<br>OEM data<br>OEM data<br>OEM data |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                              |                                                                                                                                                                                                                                                                                            | RS422 Driver                                                             | Page 25                                                                                                                                                                               |

| <b>Test</b><br>TEST:<br>PROGZAP:                                             | Test mode<br>Activation of programming routine                                                                                                                                                                                                                                             | ENSSI:<br>CFGO:<br>TRIHL:<br>CFGDR:                                      | Activation of SSI mode<br>Configuration of output mode<br>Tristate high-side/low-side driver<br>Driver property                                                                       |

|                                                                              |                                                                                                                                                                                                                                                                                            | BiSS Interface                                                           | <b>e</b> Page 26                                                                                                                                                                      |

| <b>Sine-to-Digita</b><br>CFGRES:<br>CFGZPOS:                                 | I Converter Page 22<br>Resolution of sine-to-digital converter<br>Zero point for position                                                                                                                                                                                                  | ENSSI:<br>CFGTOS:<br>CFGTOB:                                             | Activation of SSI mode<br>Programmable BiSS timeout<br>Permanent program. BiSS timeout                                                                                                |

| CFGHYS:<br>CFGDIR:<br>CFGMTD:                                                | Hysteresis sine-to-digital converter<br>Rotating direction reversal<br>Frequency at AB                                                                                                                                                                                                     | OTP Program<br>ENHC <sup>2</sup> :                                       | ming Page 29<br>Enable high current during ZAP-diode<br>read (iC-MHL200_3 and later)                                                                                                  |

| CFGSU:                                                                       | Behavior during start-up                                                                                                                                                                                                                                                                   | CFGPROT:                                                                 | Write/read protection memory                                                                                                                                                          |

|                                                                              |                                                                                                                                                                                                                                                                                            |                                                                          |                                                                                                                                                                                       |

moving magnetic target

Rev E1, Page 14/33

Χ

### **BASIC OPERATION**

The iC-MHL200 uses an array of hall sensors to detect the local variation of the magnetic field emerging from a magnetic target. The target could be a magnetic tape with periodic varying polarity and a pitch (NS spacing) of 2 mm to match the iC-MHL200 sensor period P of 4 mm. An example for linear position sensing is shown in Figure 6.

Figure 6: Typical arrangement of a magnetic tape to iC-MHL200

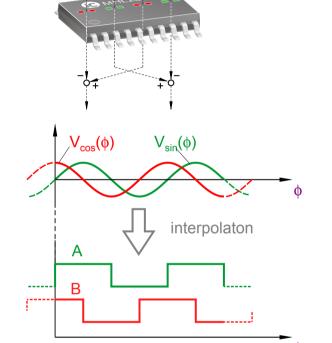

From the periodic magnetic field delivered by the target, the hall sensor array generates internal sensor signals which are then further processed and passed to the interpolator to generate incremental position data, as shown in Figure 7.

Figure 7: Signal generation and position data output

### HALL SENSORS: Position and Analog Signals

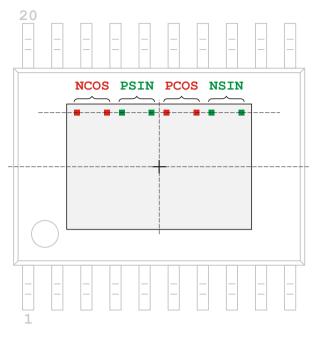

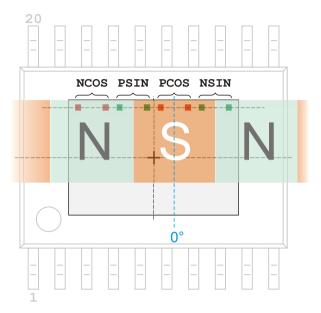

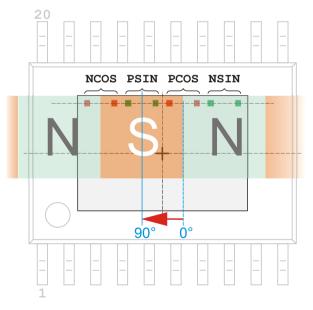

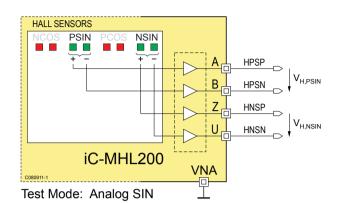

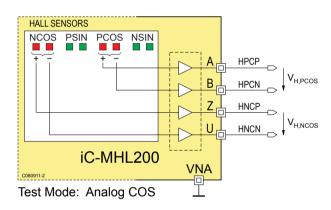

The magnetic sensor array is placed in a line at the upper edge of the chip as shown in Figure 8. Each of the four sensor location (NCOS, PSIN, PCOS and NSIN) are equally spaced apart and are based on a pair of Hall sensors. Each Hall sensor pair provides a Hall output signal from the mean value of the two single sensors a pair consists of, thus representing the magnetic field strength at the center of each pair.

When a magnetic target is placed on top of the iC-MHL200 package, the resulting magnetic field generates corresponding Hall voltages. If a magnetic south

pole is on top of a Hall sensor pair, the resulting Hall voltage is positive, whereas a magnetic north pole provides a negative one.

To provide accurate sensor signals, the magnetic target must consist of a periodic arrangement of north and south poles with a pitch (spacing NS) of 2 mm. The magnetic field distribution thus has a periodic variation of 4 mm, matching the Hall sensor array period exactly. Usually, a magnetic tape with magnetized north-south pattern is used together with the iC-MHL200.

Rev E1, Page 15/33

Figure 8: Position of the Hall sensors

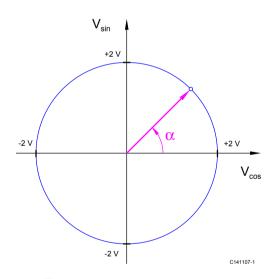

The field distribution can be approximately described as a sinusoidal variation of the magnetic field strength B along the target. As mentioned before, the iC-MHL200 provides analog sensor signals  $V_{SIN}$  and  $V_{COS}$  which represents the linear position of the tape with respect to the chip. The signals are internal but can be made externally available for test purposes (see the description of calibration procedure).

These signals are derived from the output signal difference of the complementary sensor pairs (PSIN/NSIN for the sine signal, PCOS/NCOS for the cosine signal) resulting in

$V_{SIN} = V_{PSIN} - V_{NSIN}$

and

$V_{COS} = V_{PCOS} - V_{NCOS}$ .

Since the field distribution repeats periodically every 4 mm, an absolute position value can be defined only within a range of one magnetic period. Electrically, the sensor signals are repeating every 360° for every target movement of 4 mm.

By definition, the electrical zero position (within one period) is given by the corresponding angular zero value  $\phi = 0$  where V<sub>sin</sub> is zero and V<sub>cos</sub> is at its maximum value. The mechanical zero-position location of the tape with respect to the iC-MHL200 is shown in Figure 9.

Figure 9: Zero angular position of the magnetic target. Center of south pole is aligned to the PCOS sensor pair

The definition of a specific moving direction can be made by comparing the mechanical position with the corresponding electrical angular value. To obtain increasing angular position values, the magnetic tape has to be moved to the left (when looking on top of the chip/package) as shown in Figure 10 where the tape has been shifted 1 mm to the left, as compared to Figure 9.

Figure 10: Position of the magnetic target at 90° electrical position. Center of south pole is aligned to the PSIN sensor pair

## HALL SIGNAL CONDITIONING

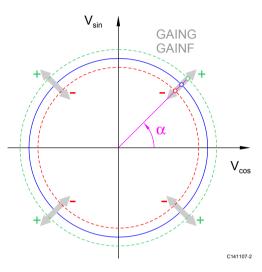

The iC-MHL200 system has a signal calibration function that can compensate for the signal and adjustment errors. The Hall signals are amplified in two steps. First, the range of the field strength within which the Hall sensor is operated must be roughly selected. The first amplifier stage can be programmed in the following ranges:

| GAING(1:0) | Addr. 0x00; bit 7:6 |

|------------|---------------------|

| Value      | Coarse Gain         |

| 0x00       | 5-fold              |

| 0x01       | 10-fold             |

| 0x02       | 15-fold             |

| 0x03       | 20-fold             |

Table 2: Range selection for Hall signal amplification

The operating range can be specified in advance in accordance with the temperature coefficient and the magnet distance. The integrated amplitude control can correct the signal amplitude between 1 and 20 via another amplification factor. Should the control reach the range limits, a different signal amplification must be selected via GAING.

| GAINF(5:0) | Addr. 0x00; bit 5:0                  |

|------------|--------------------------------------|

| Value      | Fine Gain                            |

| 0x000x02   | 1.098                                |

| 0x03       | 1.150                                |

|            | $exp(\frac{ln(20)}{64} \cdot GAINF)$ |

| 0x3E0x3F   | 18.213                               |

Table 3: Hall signal amplification

The second amplifier stage can be varied in an additional range. With the amplitude control (ENAC = 0) deactivated, the amplification in the GAINF register is used. With the amplitude control (ENAC = 1) activated, the GAINF register bits have no effect.

| GCC(6:0) | Addr. 0x01; bit 6:0                           |

|----------|-----------------------------------------------|

| Value    | Function                                      |

| 0x00     | 1.000                                         |

| 0x01     | 1.0015                                        |

|          | $exp(\frac{ln(20)}{2048} \cdot GCC)$          |

| 0x3F     | 1.0965                                        |

| 0x40     | 0.9106                                        |

|          | $exp(-\frac{ln(20)}{2048} \cdot (128 - GCC))$ |

| 0x7F     | 0.9985                                        |

Table 4: Amplification calibration cosine

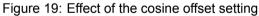

The GCC register is used to correct the sensitivity of the sine channel in relation to the cosine channel. The cosine amplitude can be corrected within a range of approximately  $\pm 10$  %.

| ENAC  | Addr. 0x01; bit 7             |  |

|-------|-------------------------------|--|

| Value | Description                   |  |

| 0x0   | Amplitude control deactivated |  |

| 0x1   | Amplitude control active      |  |

Table 5: Activation of amplitude control

The integrated amplitude control can be activated with the ENAC bit. In this case the differential signal amplitude is adjusted to 4 Vpp and the values of GAINF have no effect here.

Figure 11: Definition of differential amplitude

After switch-on the amplification is increased until the setpoint amplitude is reached. The amplification is automatically corrected in case of a change in the input amplitude by increasing the distance between the magnet and the sensor, in case of a change in the supply voltage or a temperature change. The sine signals are therefore always converted into high-resolution quadrature signals at the optimum amplitude.

| VOSS(6:0) | Addr. 0x02; bit 6:0 |

|-----------|---------------------|

| VOSC(6:0) | Addr. 0x03; bit 6:0 |

| Value     | Offset correction   |

| 0x00      | 0 mV                |

| 0x01      | 1 mV                |

|           |                     |

| 0x3F      | 63 mV               |

| 0x40      | 0 mV                |

| 0x41      | -1 mV               |

|           |                     |

| 0x7F      | -63 mV              |

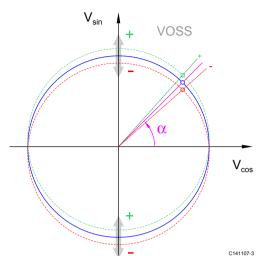

Table 6: Offset calibration for sine and cosine

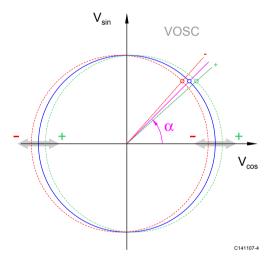

Should there be an offset in the sine or cosine signal that, among other things, can also be caused by an inexactly adjusted magnet, then this offset can be corrected by the VOSS and VOSC registers. The output voltage can be shifted by  $\pm 63$  mV in each case to compensate for the offset.

Rev E1, Page 17/33

| PRM   | Addr. 0x03; bit 7              |  |

|-------|--------------------------------|--|

| Value | Function                       |  |

| 0x0   | Energy-saving mode deactivated |  |

| 0x1   | Energy-saving mode activated   |  |

Table 7: Energy-saving mode

In the energy-saving mode the current consumption of the Hall sensors can be quartered. This also reduces the maximum rotating frequency by a factor of 4.

| CIBM(3:0) | Addr. 0x04; bit 3:0 |

|-----------|---------------------|

| Value     | Function            |

| 0x0       | -40 %               |

|           |                     |

| 0x8       | 0 %                 |

| 0x9       | +5 %                |

|           |                     |

| 0xF       | +35 %               |

Table 8: Calibration of bias current

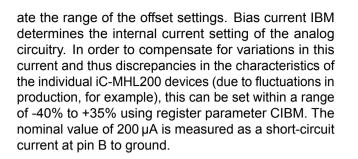

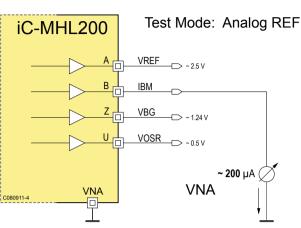

In the test mode (TEST = 0x43) the internal bias current IBM can be measured on pin B vs pin VNA and changed via register CIBM to achieve a nominal value of  $200 \,\mu$ A.

**Note:** CIBM is pre-programmed to the zapping ROM by iC-Haus and needs no further adjustment.

| HCLH  | Addr. 0x04; bit 7 |

|-------|-------------------|

| Value | Frequency         |

| 0x0   | 250 kHz           |

| 0x1   | 500 kHz           |

Table 9: Activation of high Hall clock pulse

The switching-current hall sensors can be operated at two frequencies. At 500 kHz the sine has twice the number of support points. This setting is of interest at high magnetic input frequencies beyond 500 Hz (equivalent to 2 m/s comparable to Item 102).

Rev E1, Page 18/33

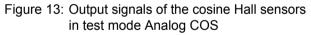

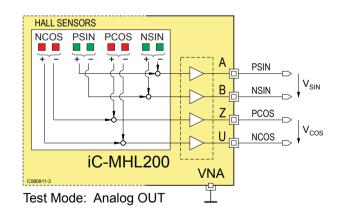

### **TEST: Modes for Signal Calibration**