## Rev B1, Page 1/14

### FEATURES

- High synchronism and technical reliability due to monolithic construction featuring on-chip photosensors

- ♦ Scanning with constant-light evaluation at a pitch of 600 µm

- Photocurrent amplifiers with high cut-off frequency

- Adjustable illumination control with 40 mA LED driver ensures constant receiver power over life

- Monitoring of safe operating range with alarm message (e.g. EOL message on LED control error)

- Serial data output via extended SSI interface

- Parallel 5 bit data output as Gray or binary code

- Adjustable phase of MSB track selects for sense of Gray code direction

- Selectable all-track bit inversion

- Supports chain circuits of multiple devices including synchronisation options

- Integrated test aids

- ♦ Single 4 to 5.5 V supply, low power consumption

- Extended operating temperature range of -40 to 125 °C

# APPLICATIONS

- Scanning with constant-light evaluation for optical encoders

- Low-res singleturn encoders

- Multiturn encoders

## PACKAGES

16-pin BLCC 7 mm x 7 mm RoHS compliant

32-pin optoQFN 5 mm x 5 mm RoHS compliant

# **iC-LV** 5-BIT OPTO ENCODER

## DESCRIPTION

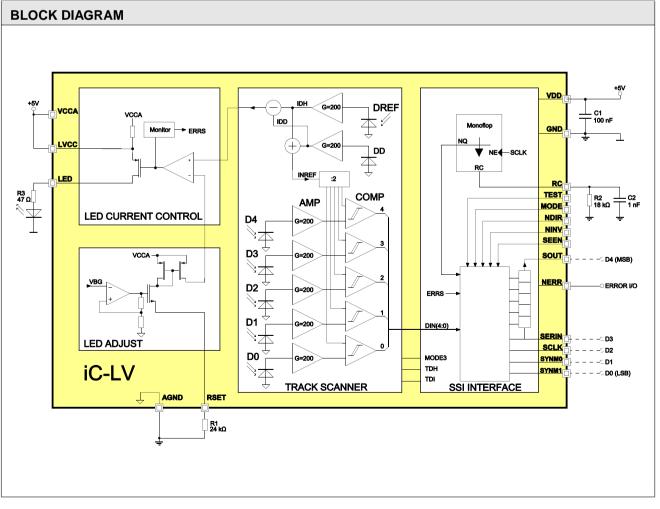

iC-LV is an optoelectronic encoder IC for absolute linear and angle measuring systems such as glass scales and shaft encoders, for example. Photosensors, amplifiers and comparators for 5 tracks at a pitch of  $600 \,\mu\text{m}$  and a reference photosensor operating the LED power control are monolithically integrated on the chip.

The internal comparator outputs switch to high when the amplified photocurrents exceed a given threshold (constant light evaluation). This threshold can be adjusted using an external resistor at RSET; alternatively, if RSET is not wired an internal resistor is used.

The internal or external resistor also establishes a setpoint for the LED current control which irrespective of temperature or the effects of aging keeps the optical receive power constant. A driver stage enables either a transmitting LED with a series resistor

to be directly connected to the device or operates an external transistor to generate higher currents.

Track information can be read out in parallel (either in Gray or binary code) or serially via an SSI protocol. Here, any number of iC-LVs can be cascaded and synchronized with one another; data is then output as a binary word (requiring Gray code discs).

A watchdog generates an alarm message via the error output if the LED current control range is exceeded. The open-drain error output can be wired to a bus; the signal is then low active. The serial data output can also be complemented by the error bit.

All inputs and outputs are protected against destruction by ESD. Two different test modes can be selected by pin and permit a complete test of functions with the exception of the photosensors.

### PACKAGING INFORMATION

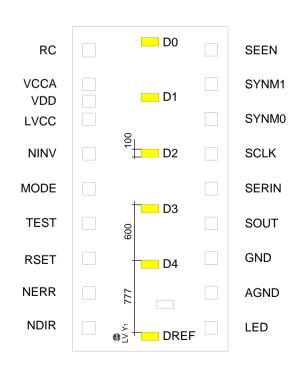

### PAD LAYOUT

## PAD FUNCTIONS No. Name Function

| RC    | RC Network for SSI Monoflop              |

|-------|------------------------------------------|

|       | (wiring is optional)                     |

| VCCA  | +4+5.5 V Analog Supply Voltage           |

| VDD   | +4+5.5 V Digital Supply Voltage          |

| LVCC  | +4+5.5 V LED Driver Supply Voltage       |

| NINV  | Bit-wise Inversion Input (low active)    |

| MODE  | Operating Mode Selection Input           |

| TEST  | Test Mode Enable Input (high active)     |

| RSET  | LED Power Control Adjustment             |

|       | (wiring is optional)                     |

| NERR  | Error Output (low active)                |

| NDIR  | Direction Input (low active)             |

| LED   | LED Power Control Output                 |

|       | (high-side current source)               |

| AGND  | Analog Ground                            |

| GND   | Digital Ground                           |

| SOUT  | Serial Data Output (SSI)                 |

|       | / Data Output D4                         |

| SERIN | Serial Data Input (SSI) / Data Outp. D3  |

| SCLK  | Clock Input (SSI) / Data Output D2       |

| SYNM0 | Synchronisation Mode Input               |

|       | / Data Output D1                         |

| SYNM1 | Synchronisation Mode Input               |

|       | / Data Output D0                         |

| SEEN  | Serial Error Bit Enable Inp. (high act.) |

Rev B1, Page 3/14

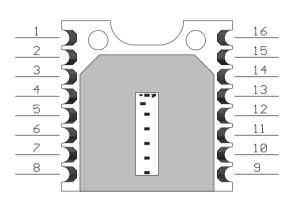

# **PIN CONFIGURATION BLCC LV4C**

#### **PIN FUNCTIONS**

#### N

| No. | Name               | Function                                 |

|-----|--------------------|------------------------------------------|

| 1   | LED                | LED Power Control Output                 |

|     |                    | (high-side current source)               |

| 2   | GND                | Ground                                   |

| 3   | SOUT               | Serial Data Output (SSI)                 |

|     |                    | / Data Output D4                         |

| 4   | SERIN              | Serial Data Input (SSI) / Data Outp. D3  |

| 5   | SCLK               | Clock Input (SSI) / Data Output D2       |

| 6   | SYNM0              | Synchronisation Mode Input               |

|     |                    | / Data Output D1                         |

| 7   | SYNM1              | Synchronisation Mode Input               |

|     |                    | / Data Output D0                         |

| 8   | SEEN               | Serial Error Bit Enable Inp. (high act.) |

| 9   | n.c. <sup>1)</sup> |                                          |

| 10  | VDD                | +4+5.5 V Supply Voltage                  |

| 11  | NINV               | Bit-wise Inversion Input (low active)    |

| 12  | MODE               | Operating Mode Selection Input           |

- 13 TEST Test Mode Enable Input (high active) 14 RSET LED Power Control Adjustment (wiring is optional)

- 15 NERR Error Output (low active)

- 16 NDIR Direction Input (low active)

For dimensional specifications refer to the package datasheet iC-LV BLCC LV4C, available separately.

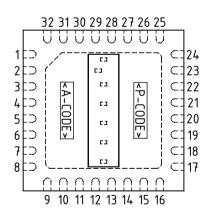

### **PIN CONFIGURATION oQFN32-5x5**

### **PIN FUNCTIONS**

#### No. Name Function

| 1  | LED                | LED Power Control Output<br>(high-side current source) |

|----|--------------------|--------------------------------------------------------|

| 2  | GND                | Ground                                                 |

| 3  | SOUT               | Serial Data Output (SSI)                               |

| 4  |                    | / Data Output D4                                       |

| -  | SERIN              | Serial Data Input (SSI) / Data Outp. D3                |

|    | SCLK               | Clock Input (SSI) / Data Output D2                     |

| 6  | SYNM0              | , i                                                    |

| _  | <b>.</b>           | / Data Output D1                                       |

| 7  | SYNM1              |                                                        |

|    |                    | / Data Output D0                                       |

|    | SEEN               | Serial Error Bit Enable Inp. (high act.)               |

| 9  | n.c. <sup>1)</sup> |                                                        |

| 18 | VDD                | +4+5.5 V Supply Voltage                                |

| 19 | NINV               | Bit-wise Inversion Input (low active)                  |

| 20 | MODE               | Operating Mode Selection Input                         |

| 21 | TEST               | Test Mode Enable Input (high active)                   |

| 22 | RSET               | LED Power Control Adjustment                           |

|    |                    | (wiring is optional)                                   |

| 23 | NERR               | Error Output (low active)                              |

| 24 | NDIR               | Direction Input (low active)                           |

| 25 | n.c. <sup>1)</sup> | • • •                                                  |

|    | BP                 | Backside paddle <sup>2)</sup>                          |

|    |                    | •                                                      |

IC top marking: <P-CODE> = product code, <A-CODE> = assembly and lot code (subject to changes);

1) Pin numbers marked n.c. are not in use.

2) The backside paddle may have a single link to GND. A current flow across the paddle is not permissible.

Rev B1, Page 4/14

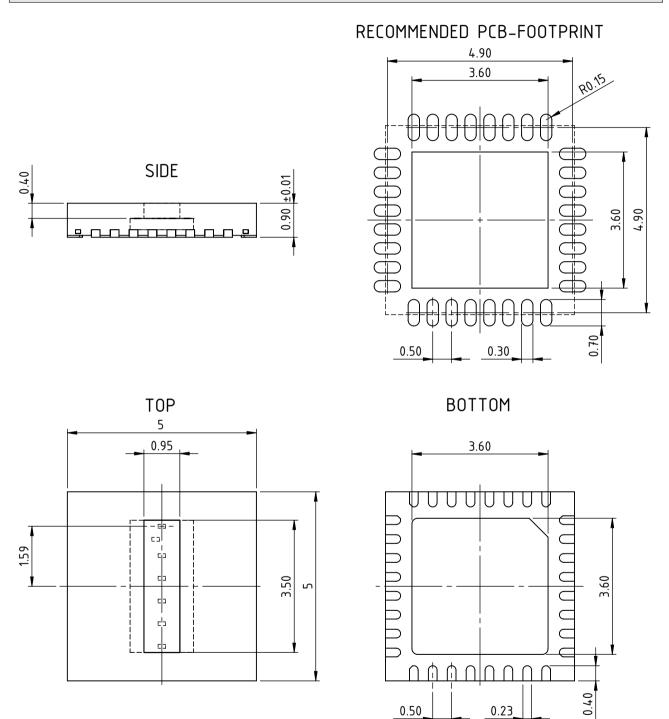

### PACKAGE DIMENSIONS oQFN32-5x5

All dimensions given in mm. Tolerances of form and position according to JEDEC MO-220. Tolerance of sensor pattern:  $\pm 70 \mu m$  /  $\pm 1^{\circ}$  (with respect to center backside pad). Maximum molding excess  $\pm 20 \mu m$  /  $-75 \mu m$  versus surface of glass/reticle.

dra\_oqfn32-5x5-2\_lv\_y1\_pack\_1, 10:1

Rev B1, Page 5/14

# **ABSOLUTE MAXIMUM RATINGS**

These ratings do not imply operating conditions; functional operation is not guaranteed. Beyond these ratings device damage may occur.

| ltem | Symbol | Parameter                                                                                                          | Conditions                                        |      |               | Unit |

|------|--------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------|---------------|------|

| No.  |        |                                                                                                                    |                                                   | Min. | Max.          |      |

| G001 | V()    | Voltage at VCCA                                                                                                    |                                                   | 0.3  | 6             | V    |

| G002 | V()    | Voltage at VDD                                                                                                     |                                                   | VCCA | VCCA          | V    |

| G003 | V()    | Voltage at LVCC, LED, SOUT, SERIN,<br>SCLK, SYNM0, SYNM1, SEEN, NDIR,<br>NERR, RSET, TEST, MODE, NINV, RC          |                                                   | -0.3 | VCCA +<br>0.3 | V    |

| G004 | Ic()   | Clamp Diode Current in LED, SOUT,<br>SERIN, SCLK, SYNM0, SYNM1,<br>SEEN, NDIR, NERR, RSET, TEST,<br>MODE, NINV, RC | SERIN, SCLK, SYNM0, SYNM1 with input<br>function  | -4   | 4             | mA   |

| G005 | 1()    | Current in SOUT, SERIN, SCLK,<br>SYNM0, SYNM1, RSET, RC                                                            | SERIN, SCLK, SYNM0, SYNM1 with output<br>function | -4   | 4             | mA   |

| G006 | I()    | Current in LVCC to LED                                                                                             | $V(LVCC) \leq VCCA$                               | 0    | 50            | mA   |

| G007 | Vd()   | ESD Susceptibility at all pins                                                                                     | HBM, 100 pF discharged through $1.5  k\Omega$     |      | 2             | kV   |

| G008 | Tj     | Junction Temperature                                                                                               |                                                   | -40  | 125           | °C   |

| G009 | Ts     | Chip Storage Temperature                                                                                           |                                                   | -40  | 125           | °C   |

## THERMAL DATA

Operating Conditions: VCCA, VDD, LVCC = 4...5.5 V

| ltem | Symbol | Parameter                                | Conditions                                                                                                                                                                                                        |      |      |            | Unit     |

|------|--------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------------|----------|

| No.  |        |                                          |                                                                                                                                                                                                                   | Min. | Тур. | Max.       |          |

| T01  | Та     | Operating Ambient Temperature Range      | oQFN32-5x5<br>BLCC LV4C: refer to package specification                                                                                                                                                           | -40  |      | 110        | °C       |

| T02  | Ts     | Permissible Storage Temperature<br>Range | oQFN32-5x5<br>BLCC LV4C: refer to package specification                                                                                                                                                           | -40  |      | 110        | °C       |

| T03  | Трк    | Soldering Peak Temperature<br>oQFN32-5x5 | tpk < 20 s, convection reflow<br>tpk < 20 s, vapor phase soldering<br>MSL 5A (max. floor live 24 h at 30 $^{\circ}$ C and<br>50 $^{\circ}$ RH)<br>Please refer to customer information file No. 7<br>for details. |      |      | 245<br>230 | °C<br>°C |

| T04  | Tpk    | Soldering Peak Temperature<br>BLCC LV4C  | refer to package specification                                                                                                                                                                                    |      |      |            |          |

Rev B1, Page 6/14

# ELECTRICAL CHARACTERISTICS

| ltem<br>No. | Symbol                                                 | Parameter                                                                                                                 | Conditions                                                                                   | Min. | Тур.         | Max.       | Unit               |

|-------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|--------------|------------|--------------------|

| Total       | Device                                                 | 1                                                                                                                         | 1                                                                                            |      |              | J          | 11                 |

| 001         | VDD                                                    | Permissible Supply Voltage<br>VCCA, VDD, LVCC                                                                             |                                                                                              | 4.0  | 5            | 5.5        | V                  |

| 002         | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |                                                                                                                           |                                                                                              | 2    | 5            | mA         |                    |

| 003         | Vcz()hi                                                | Clamp Voltage hi at all pins versus GNDA                                                                                  | I() = 4 mA                                                                                   |      |              | 11         | V                  |

| 004         | Vc()hi                                                 | Vc()hi Clamp Voltage hi at inputs:<br>RC, NINV, MODE, TEST, RSET,<br>NERR, NDIR, SEEN, SYNM1,<br>SYNM0, SCLK, SERIN, SOUT |                                                                                              | 0.3  |              | 1.2        | V                  |

| 005         | Vc()lo                                                 | Clamp Voltage lo at all pins                                                                                              | I() = -4 mA                                                                                  | -1.2 |              | -0.3       | V                  |

| TTL I       | nputs: SYN                                             | IM1, SYNM0, SCLK, SERIN, SEEN                                                                                             | , NDIR, TEST, MODE, NINV                                                                     |      |              |            | 0                  |

| 006         | Vt()hi                                                 | Threshold Voltage hi                                                                                                      | MODE = hi                                                                                    |      |              | 2          | V                  |

| 007         | Vt()lo                                                 | Threshold Voltage lo                                                                                                      | MODE = hi                                                                                    | 0.8  |              |            | V                  |

| 800         | Vt()hys                                                | Threshold Voltage Hysteresis                                                                                              | MODE = hi                                                                                    | 300  | 500          |            | mV                 |

| 009         | lpu()                                                  | Pull-up Current in<br>SCLK, SERIN, SEEN, NDIR,<br>MODE, NINV                                                              | V() = 0 VCCA – 1 V,<br>MODE = hi                                                             | -62  | -30          | -4         | μA                 |

| 010         | lpu()                                                  | Pull-up Current in<br>SYNM1, SYNM0                                                                                        | V() = 0 VCCA - 1 V,<br>MODE = hi                                                             | -80  |              | -4         | μA                 |

| 011         | lpd()                                                  | Pull-down Current in TEST                                                                                                 | V() = 1 V VCCA, MODE = hi                                                                    | 3    | 31           | 75         | μA                 |

| Outpu       | uts D0 to D                                            | 4: SYNM1, SYNM0, SCLK, SERIN,                                                                                             | SOUT                                                                                         |      |              |            |                    |

| 012         | Vs()hi                                                 | Saturation Voltage hi                                                                                                     | Vs()hi = VDD - V(); I() = -4 mA, MODE = Io                                                   |      |              | 500        | mV                 |

| 013         | Vs()lo                                                 | Saturation Voltage lo                                                                                                     | l() = 4 mA<br>l() = 1.6 mA                                                                   |      |              | 500<br>400 | mV<br>mV           |

| Error       | Output NE                                              | RR                                                                                                                        |                                                                                              |      |              |            |                    |

| 014         | Vs()lo                                                 | Saturation Voltage lo                                                                                                     | I() = 4 mA<br>I() = 1.6 mA                                                                   |      |              | 500<br>400 | mV<br>mV           |

| 015         | R()pu                                                  | Permissible Pull-up Load                                                                                                  |                                                                                              |      | 10           |            | kΩ                 |

| Curre       | nt Compar                                              | ators, Tracks 04                                                                                                          |                                                                                              |      |              |            |                    |

| 301         | IDREF                                                  | Reference Sensor Photocurrent                                                                                             |                                                                                              |      | 100          |            | nA                 |

| 302         | IDD                                                    | Compensation Sensor Dark Cur-<br>rent                                                                                     |                                                                                              |      | 20           |            | pА                 |

| 303         | Hys                                                    | Switch Hysteresis Referred to<br>Reference Current IDREF                                                                  | I(D04) = IDD IDREF                                                                           | 14   | 17           | 20         | %                  |

| Photo       | sensors a                                              | nd Amplifiers D04, DREF                                                                                                   |                                                                                              |      |              |            |                    |

| 401         | $S(\lambda)$                                           | Spectral Sensitivity                                                                                                      | $\lambda$ = 880 nm                                                                           |      | 0.3          |            | A/W                |

| 402         | $\lambda$ ar                                           | Spectral Application Range                                                                                                | $Se(\lambda ar) = 0.1 \times S(\lambda)max$                                                  | 400  |              | 1050       | nm                 |

| 403         | Aph()                                                  | Active Photosensor Area                                                                                                   |                                                                                              |      | 0.2 x<br>0.1 |            | mm <sup>2</sup>    |

| 404         | E()mx                                                  | Permissible Irradiance                                                                                                    | application range                                                                            |      |              | 1000       | µW/cm <sup>2</sup> |

| 405         | fc                                                     | Upper Cut-off Frequency                                                                                                   | sine waveform,<br>I(D04) = 880 nA, I(DREF) = 80 nA                                           | 200  |              |            | kHz                |

| 406         | ∆tp()                                                  | Propagation Delay Difference<br>(Delay Skew)                                                                              | square waveform, R(RSET/AGND) = $24 \text{ k}\Omega$ ,<br>I(D04) = 8100 nA, I(DREF) = 100 nA |      |              | 0.5        | μs                 |

| 407         | CM()                                                   | Common Mode Referred to Reference Photocurrent I(DREF)                                                                    |                                                                                              | 0.85 | 1            | 1.15       |                    |

Rev B1, Page 7/14

# **ELECTRICAL CHARACTERISTICS**

| ltem   | Symbol      | Parameter                              | Conditions                                                           |      |              |      | Unit            |

|--------|-------------|----------------------------------------|----------------------------------------------------------------------|------|--------------|------|-----------------|

| No.    |             |                                        |                                                                      | Min. | Тур.         | Max. |                 |

| LED F  | Power Conti | rol and DREF Reference Sensor          |                                                                      |      |              |      |                 |

| 501    | Aph()       | Active Photosensor Area DREF           |                                                                      |      | 0.2 x<br>0.1 |      | mm <sup>2</sup> |

| 502    | I(LED)      | Permissible LED Output Current         |                                                                      | 0    |              | 40   | mA              |

| 503    | Vs(LED)     | Saturation Voltage at LED              | I(LED) = 40 mA                                                       |      |              | 1.1  | V               |

| 504    | tr(LED)     | LED Current Rise Time                  | I(LED) = 0100 %                                                      |      | 60           | 1500 | μs              |

| 505    | R()         | Link Resistance LVCC to VDD            |                                                                      | 2    | 5            | 10   | kΩ              |

| Mono   | flop RC     |                                        |                                                                      |      |              |      |                 |

| 601    | C(RC)       | Permissible Capacitor at RC            |                                                                      | 0.1  |              | 1000 | pF              |

| 602    | R(RC)       | Permissible Resistor at RC             |                                                                      | 15   |              | 1000 | kΩ              |

| 603    | tmf         | Monoflop Time                          | R2 = 1 nF, C2 = $18 k\Omega$ ,<br>tmf = 1.16 x R x C (+/- 15%)       | 16   | 21           | 24   | μs              |

| 604    | tmf         | Monoflop Time                          | no external RC network                                               | 11.5 | 21           | 29.5 | μs              |

| SSI In | terface     |                                        | 1                                                                    |      |              |      |                 |

| 701    | f(SCLK)     | Permissible Clock Rate at SCLK         |                                                                      |      |              | 2    | MHz             |

| 702    | tp()        | Propagation Delay SCLK to SOUT         |                                                                      |      | 85           |      | ns              |

| 703    | tp()        | Propagation Delay SERIN to SOUT        | mode Sync Out                                                        |      | 85           |      | ns              |

| 704    | tp()pwr-up  | Data Availability After Power-Up       |                                                                      |      | 2            |      | ms              |

| Analo  | g Test Mod  | e SYNM0, SYNM1                         |                                                                      |      |              |      |                 |

| 801    | CR1()       | Test Current Ratio<br>I(SYNM1)/I(D04)  | TEST = hi, MODE = lo:<br>analog test mode active, $I() = 2200 \mu A$ |      | 1000         |      |                 |

| 802    | CR2()       | Test Current Ratio<br>I(SYNM0)/I(DREF) | TEST = hi, MODE = lo:<br>analog test mode active, I() = 2200 μA      |      | 1000         |      |                 |

| Contr  | ol Adjustmo | ent RSET                               | J                                                                    |      |              |      |                 |

| E01    | V()         | Reference Voltage                      | I(RSET) = -10020 μA                                                  | 0.95 | 1.16         | 1.25 | V               |

| E02    | Ibias()     | Permissible Bias Current               |                                                                      | -100 |              | -20  | μA              |

| E03    | Ibias()     | Equivalent Internal Bias Current       | Tj = 27 °C, RSET open                                                |      | 50           |      | μA              |

| E04    | lsc()       | Short-Circuit Current                  | V(RSET) = 0 V                                                        |      | 1.3          | 2.6  | mA              |

### Rev B1, Page 8/14

# **OPERATING REQUIREMENTS: Logic**

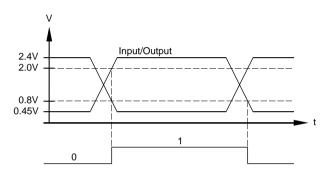

Operating Conditions: VCCA, VDD, LVCC = 4 ... 5.5 V, Tj = -40 ... +125  $^{\circ}$ C, input levels lo = 0 ... 0.45 V, hi = 2.4 V ... VDD, see Fig. 1 for reference levels.

| Item | Symbol            | Parameter                                                | Conditions   |      |      | Unit |

|------|-------------------|----------------------------------------------------------|--------------|------|------|------|

| No.  |                   |                                                          |              | Min. | Max. |      |

| 1001 | t <sub>set</sub>  | Setup Time: SERIN stable before SCLK hi $\rightarrow$ lo | mode No Sync | 30   |      | ns   |

| 1002 | t <sub>hold</sub> | Hold Time: SERIN stable after SCLK hi $\rightarrow$ lo   | mode No Sync | 30   |      | ns   |

# **OPERATING MODES AND PIN FUNCTIONS**

|       | Parallel Output<br>Mode                                                                          |                                                  | Output<br>ode                | Analog Test<br>Mode                                  | -                               | al Test<br>ode               |  |

|-------|--------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------|------------------------------------------------------|---------------------------------|------------------------------|--|

|       | MODE = 0<br>TEST = 0                                                                             | MOD<br>TES                                       | T = 0                        | MODE = 0<br>TEST = 1                                 | TES                             | DE = 1<br>T = 1              |  |

|       |                                                                                                  | SYNM0 = X<br>SYNM1 = 1                           | SYNM0 = X<br>SYNM1 = 0       |                                                      | SYNM0 = X<br>SYNM1 = 1          | SYNM0 = X<br>SYNM1 = 0       |  |

| Pin   |                                                                                                  | No Sync /<br>No Svnc Binarv                      | Sync Out /<br>SSI Out        |                                                      | No Sync                         | Sync Out /<br>SSI Out        |  |

| LED   | LED Power Cont                                                                                   | rol Output (high-                                | side current sou             | ırce)                                                |                                 |                              |  |

| AGND  | Analog Ground (reference for RC and RSET attachments)                                            |                                                  |                              |                                                      |                                 |                              |  |

| GND   | Digital Ground                                                                                   |                                                  |                              |                                                      |                                 |                              |  |

| SOUT  | Data Output D4<br>(MSB)                                                                          |                                                  | ta Output<br>terface)        | Signal Output for<br>Switch Threshold<br>Measurement |                                 | ta Output<br>terface)        |  |

| SERIN | Data Output D3                                                                                   |                                                  | Serial                       | Data Input (SSI Inte                                 | erface)                         |                              |  |

| SCLK  | Data Output D2                                                                                   |                                                  | Clo                          | ck Input (SSI Interfa                                | ace)                            |                              |  |

| SYNM0 | Data Output D1                                                                                   | Synchronisatio                                   | on Mode Input                | Test Current<br>Input DREF                           | Synchronisation Mode Input      |                              |  |

| SYNM1 | Data Output D0<br>(LSB)                                                                          | Synchronisatio                                   | on Mode Input                | Test Current<br>Input D40                            | Synchronisati                   | on Mode Input                |  |

| SEEN  | Gray/binary<br>conversion<br>(low active)                                                        | Serial Errorbit<br>Enable Input<br>/ no function | Configuration of Phase Shift | no function                                          | Serial Errorbit<br>Enable Input | Configuration of Phase Shift |  |

| RC    | RC Network for M                                                                                 | Nonoflop                                         |                              |                                                      |                                 |                              |  |

| VCCA  | +4 +5.5 V Ana                                                                                    | log Supply Volta                                 | age                          |                                                      |                                 |                              |  |

| VDD   | +4 +5.5 V Digi                                                                                   | tal Supply Voltag                                | ge                           |                                                      |                                 |                              |  |

| LVCC  | +4 +5.5 V LED                                                                                    | Driver Supply \                                  | /oltage                      |                                                      |                                 |                              |  |

| NINV  | Bit-wise Inversion                                                                               | n Input (low activ                               | /e)                          |                                                      |                                 |                              |  |

| MODE  | Operating Mode                                                                                   | Selection Input                                  |                              |                                                      |                                 |                              |  |

| TEST  | Test Mode Enabl                                                                                  | le Input (high ac                                | tive)                        |                                                      |                                 |                              |  |

| RSET  | LED Power Cont                                                                                   | rol Adjustment                                   |                              |                                                      | Γ                               |                              |  |

| NERR  | Error Output (illumination, low active)<br>Switch Threshold<br>Measurement<br>(Push-Pull Output) |                                                  |                              |                                                      |                                 |                              |  |

| NDIR  | Reversa                                                                                          | l of Rotation Dir<br>(low active)                | . Input                      | IDDQ Test<br>Enable<br>(low active)                  |                                 | tation Dir. Input<br>active) |  |

Figure 2: Operating modes and pin functions.

#### **DESCRIPTION OF FUNCTIONS**

#### Illumination control

The integrated LED power control with a driver stage keeps the photocurrent of reference photosensor DREF constant. This compensates for aging, dirt and drops in efficiency of the transmitting LED with rises in temperature.

The photocurrent of reference sensor DREF and the dark current of compensation sensor DD are amplified in the receiver. The amplified currents are subtracted from one another, yielding an actual value to feed the LED power control. The current adjusted by resistor R1 at pin RSET generates the bias for the control; the voltage at pin RSET is kept constant (see Electrical Characteristics No. E01). If pin RSET remains open an internal bias current is used which is equivalent to an external resistor of ca.  $24 \text{ k}\Omega$ .

If there is an optical feedback loop from the LED to reference sensor DREF the power driver alters the LED current until the optical power received complies with the given setpoint. The photocurrent generated by reference sensor DREF - and thus also the level of illumination for the overall system - is kept constant.

A monitoring circuit detects when and if the LED control range is overshot or undershot and signals this by switching error output NERR to low and via the error bit during serial communication (when SEEN is high and no synchronization is selected).

Resistor R3 connected in series to the transmitting LED limits the current and governs the operating limits of the LED power control.

At the same time the amplified dark current of compensation sensor DD and the reference photocurrent of sensor DREF are added together. The resulting current, named INREF, is used to provide the switching threshold for the track comparators. This enables operation of iC-LV with an external light source instead of using power-controlled LED.

### Track evaluation

The switching threshold supplied to the track comparators lies at half of INREF, ie. in the center between a full light and no light condition, and adjusts automatically to changes in illumination. This enables the device to be operated without the LED power control with a constant illumination level only. The hysteresis of the current comparators is also photocurrent tracked and increases noise immunity.

The most significant bit (MSB) can be inverted by connecting pin NDIR to ground (GND). If the pin remains open, an internal pull-up current source generates a high level. When Gray code discs are used, inverting the MSB track is tantamount to changing the direction of rotation.

#### Modes Of Operation

iC-LV has various modes of operation which are preselected using pin MODE. MODE = 0 selects operation as an optoelectronic encoder IC with a parallel output; MODE = 1 (default) makes a number of serial operating modes available.

#### Parallel Output Mode (MODE = 0)

In parallel output mode the 5 tracks with sensor D4 (MSB) to sensor D0 (LSB or least significant bit) are output in parallel to pins SYNM1 (LSB), SYNM0, SCLK, SERIN and SOUT (MSB).

The wiring of pin NDIR determines the count direction. With NDIR connected to GND the MSB is output inverted so that the count direction can be altered when reading Gray-coded discs.

By connecting pin NINV to GND the output of all bits can be inverted. If this is not required, NINV can be left open. NDIR and NINV can be used either together or independently of one another. If both pins are connected to GND all bits - with the exception of the MSB - are output inverted.

By connecting pin SEEN to GND the bits can be output in binary format following a Gray to binary code conversion. This is done after the bits have been inverted, where relevant. If pin SEEN is left unconnected the output is in Gray code.

#### Serial Output Mode (MODE = 1, default)

In serial output mode pin SCLK is the clock input hooked up to an SSI master supplying an intermittently active clock signal with a high level during idle time, pin SERIN is the serial data input and pin SOUT the serial data output.

Various serial operational modes and output formats can be configured using pins SYNM0 and SYNM1 (high when not wired).

| SYNM(1:0) |                   |                                          |

|-----------|-------------------|------------------------------------------|

| Code      | Serial Op. Modes  | Data Output Format                       |

| 11        | No Sync (default) | 5 bit Gray<br>(option: +1 error bit)     |

| 10        | No Sync Binary    | 5 bit binary                             |

| 0 1       | Sync Out          | 4 bit binary<br>(corrected by +/- 1 bit) |

| 0 0       | SSI Out           | 4 bit binary<br>(corrected by +/- 1 bit) |

Table 5: Serial Operating Modes

In **No Sync** mode an LED control error bit (low active) can be added to the serial data by releasing it via pin

Rev B1, Page 11/14

SEEN. In **No Sync Binary** mode pin SEEN has no function.

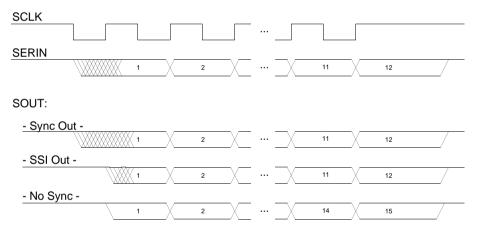

In both **No Sync** and **No Sync Binary** mode iC-LV operates without synchronization, i.e. it stores the 5 track values on the first falling edge seen at SCLK after a long idle time and then transmits the track data via pin SOUT on each of the 5 following rising edges at SCLK. At the same time pin SERIN reads in data from a prepositioned iC-LV which can then be passed on. Here, iC-LV operates as a 5-bit shift register (or 6-bit if the error bit is active during No Sync mode) whose flipflops accept input data on a falling edge and output stored data on a rising edge.

In **No Sync Binary** mode data is converted from Gray to binary before being output. In this mode of operation it is not possible to output a serial error bit; no data from SERIN is accepted on the first and second rising edge at SCLK.

If pin NDIR is connected to GND a change in count direction with Gray codes can be initiated by inverting the MSB. By connecting pin NINV to GND all track data can be output inverted. Both pins NINV and NDIR are high when not connected.

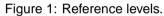

In modes **SSI out** and **Sync Out** iC-LV operates with synchronization, classing the LSB of its own code disc as a synchronization bit. The data read in from the code disc is converted into binary code and, if necessary, corrected by +1 or -1 depending on the MSB of the pre-positioned device also read in.

Each LSB has the same resolution as the MSB of the pre-positioned iC-LV, operated at a 16-fold faster speed, and is assembled so that it either trails (SEEN is high, default) or leads (SEEN is low) by up to 90°. The phase position must be configured for each individual code disc using pin SEEN (trail/lead). This phase shift applies to data converted into binary code and is not immediately visible on the code discs.

If data is read out serially and synchronized elsewhere a smaller phase shift must be adjusted. In this instance data transmission times must be taken into account.

The synchronization process ensures that synchronous with the flipping of the MSB from the prepositioned iC-LV track data is switched forward to the next data word expected on that code disc. Once the track data has been captured on the first falling edge at SLCK, the data word is synchronized with the MSB of the predecessor during the first low and first high period on the SCLK line (the MSB is possibly subject to change within this time).

Rev B1, Page 12/14

The synchronization result is switched straight through to the output so that a synchronized MSB is available for each following gear. This allows the track data to be synchronized with MSBs on the first falling as well as on the first rising edge.

In synchronization modes iC-LV functions as a 4-bit shift register, i.e. the synchronization bit is not clocked out with the track data. Serial data is read in on a falling edge and output on a rising edge. In SSI Out mode the MSB is blanked out by a high until the first rising edge and thus output on this first rising edge, making this mode SSI compatible.

Figure 3: Synchronization

If inverted Gray codes are used on the code discs a code inversion can be initiated by connecting NINV to GND. By connecting NDIR to GND the MSB bit is output inverted to reverse the count direction of the Gray code. Here it should be noted that inverting the MSB output causes a 180° change in the phase position, i.e. a trailing 90° synchronization track becomes a leading 90° track and vice versa. This can be compensated for by a suitable setting of pin SEEN or by assembling the code disc in a suitable zero position.

# **Test Modes**

iC-LV has two different test modes which are activated by connecting pin TEST to VDD. Pin MODE designates which test mode is activated. Connected to VDD (or not connected at all), this initiates the digital test mode; if connected to GND the analog test mode is selected. Analog Test Modes (MODE = 0)

**Sensor emulation and comparator switching threshold test:** To test the track evaluation and switching thresholds a test current is supplied at pin SYNM0 for reference sensor DREF and at SYNM1 for the track sensors. The current reduction ratio is 1:1000.

Alternatively, testing can be carried out by illumination as the supplied test currents are added to the photocurrents. The track to be measured at SOUT is selected via a 5-bit shift register. To this end a suitable bit stream is clocked in via SCLK (clock low active) and SERIN (level). If more than one track is selected, the comparator output signals are EXORed. The 5-bit shift register addresses track sensors D4 to D0 via bits 4 to 0. When measurement commences the shift register should be filled up with zero.

**IDDQ test:** This test is initiated by connecting pin NDIR (default high) to GND.

# Digital Test Modes (MODE = 1, open)

**Logic test:** Digital test mode is largely identical to the serial operating modes. One difference is that data input at pin SERIN is first clocked through a 5-bit shift register before being clocked through the output shift register. This enables various bit sequences to be first clocked into the test register. Following an idle time on the clock line of t > tmf (see Electrical Characteristics No. 603) the test data is stored on the first falling edge on SCLK instead of the track values.

This allows various sensor input stimuli to be generated. In the synchronized operating modes the data word is synchronized with pin SERIN as in normal operating mode. Configuration of the various serial operating modes is also as in normal operating mode. No stimuli can be clocked in in **No Sync Binary** mode.

**TP:** So that the switching thresholds of the input interfaces (SYNM0, SYNM1, SERIN, SCLK, NDIR, NINV, SEEN) can be measured the signals are EXORed and output at pin NERR. To this end pin NERR is switched as a push-pull output.

Rev B1, Page 13/14

#### **APPLICATION INFORMATION**

If a stable SSI output level is required all MSBs used in the synchronization chain must be switched to the relevant outputs on the first falling edge. The iC-LV chain should also be synchronized in its entirety before the first rising edge of SCLK.

To guarantee functionality it is sufficient for synchronization to be completed by the second falling edge of SCLK; SOUT is, however, then not stable for half a clock cycle. Despite this limitation it is also possible to synchronize with MSBs which are only output on the first rising SCLK edge (e.g. from external SSIcompatible devices).

Figure 4 gives signal patterns for a cascade of three iC-LVs.

In the synchronization modes all of the information is output after just 4 rising clock edges per chained iC-LV.

In keeping with the required SSI clock frequency the time span of the internal monoflop, used to detect idle times on the clock line, can be adjusted by externally connecting pin RC to an RC network. Should pin RC remain unconnected, tmf (Electrical Characteristics No. 603) is taken as the internal time span.

Note: iC-LV stores input data received at SERIN on the falling edge of SCLK and outputs data via SOUT on the rising edge of SCLK.

### Figure 4: SOUT in the various modes of operation.

#### **REVISION HISTORY**

| Rel | Rel.Date | Chapter                    | Modification                 | Page |

|-----|----------|----------------------------|------------------------------|------|

| A3  | 07-08-30 |                            |                              |      |

|     |          |                            |                              |      |

| Rel | Rel.Date | Chapter                    | Modification                 | Page |

| B1  | 14-07-09 | PACKAGES, THERMAL DATA     | optoQFN package supplemented | 1-5  |

|     |          | ELECTRICAL CHARACTERISTICS | Item 704 supplemented        | 7    |

|     |          | DESCRIPTION OF FUNCTIONS   | Figure 3 corrected           | 12   |

|     |          | REVISION HISTORY           | Chapter supplemented         | 13   |

iC-Haus expressly reserves the right to change its products and/or specifications. An info letter gives details as to any amendments and additions made to the relevant current specifications on our internet website www.ichaus.de/infoletter; this letter is generated automatically and shall be sent to registered users by email.

Copying - even as an excerpt - is only permitted with iC-Haus' approval in writing and precise reference to source

iC-Haus does not warrant the accuracy, completeness or timeliness of the specification and does not assume liability for any errors or omissions in these materials.

The data specified is intended solely for the purpose of product description. No representations or warranties, either express or implied, of merchantability, fitness for a particular purpose or of any other nature are made hereunder with respect to information/specification or the products to which information refers and no guarantee with respect to compliance to the intended use is given. In particular, this also applies to the stated possible applications or areas of applications of the product.

iC-Haus conveys no patent, copyright, mask work right or other trade mark right to this product. iC-Haus assumes no liability for any patent and/or other trade mark rights of a third party resulting from processing or handling of the product and/or any other use of the product.

Rev B1, Page 14/14

# **ORDERING INFORMATION**

| Туре  | Package                                                            | Order Designation |  |

|-------|--------------------------------------------------------------------|-------------------|--|

| iC-LV | 16-pin BLCC, 7 mm x 7 mm,<br>thickness 1.6 mm<br>RoHS compliant    | iC-LV BLCC LV4C   |  |

|       | 32-pin optoQFN, 5 mm x 5 mm,<br>thickness 0.9 mm<br>RoHS compliant | iC-LV oQFN32-5x5  |  |

For technical support, information about prices and terms of delivery please contact:

| iC-Haus GmbH      | Tel.: +49 (0) 61 35 - 92 92 - 0  |

|-------------------|----------------------------------|

| Am Kuemmerling 18 | Fax: +49 (0) 61 35 - 92 92 - 192 |

| D-55294 Bodenheim | Web: http://www.ichaus.com       |

| GERMANY           | E-Mail: sales@ichaus.com         |

Appointed local distributors: http://www.ichaus.com/sales\_partners