Rev B3, Page 1/26

#### **FEATURES**

- ♦ Fully differential 3-channel signal conditioning

- ♦ PGS inputs for differential and single-ended signals

- ♦ Overall gain of -3 to 57 dB, adjustable in steps of 0.08 dB

- Output referred offset range of ±1.2 V, adjustable in steps of 2 mV

- Signal bandwidth to 1 MHz and in/out latency below 1 μs

- Selectable automatic gain and offset control for encoder applications

- ♦ On-chip or off-chip temperature sensing

- ♦ Temperature drift compensation for gain and offset via programmable look-up-tables

- ♦ Short-circuit-proof outputs: 1 Vpp to  $100 \Omega$ , 2 Vpp to  $1 k\Omega$

- ♦ I<sup>2</sup>C interface to restore device setup from serial EEPROM

- ♦ Bidirectional 1-wire interface for direct RAM and EEPROM access

- ♦ Optical setup link via 1-wire interface operating a photo receiver

- ♦ Single 3.0 V to 5.5 V supply

- ♦ Operating temperature range of -40 to +125 °C

#### **APPLICATIONS**

- Programmable general purpose sensor interface

- ♦ Optical position sensors

- ♦ Magnetic position sensors

- Incremental position sensors

- Linear scales

Rev B3, Page 2/26

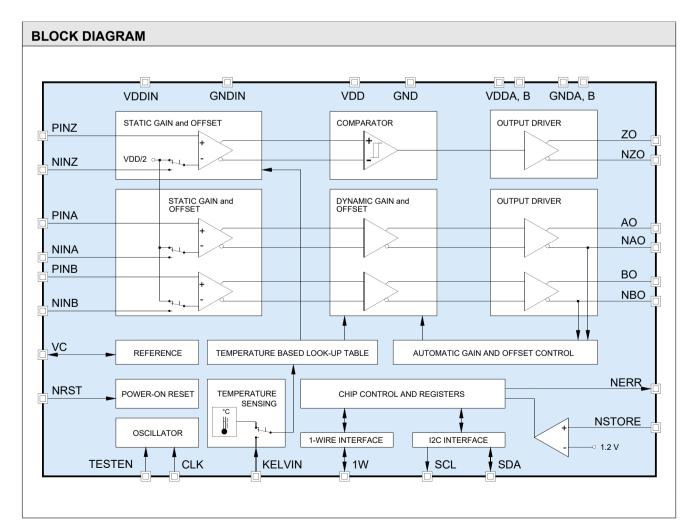

#### **DESCRIPTION**

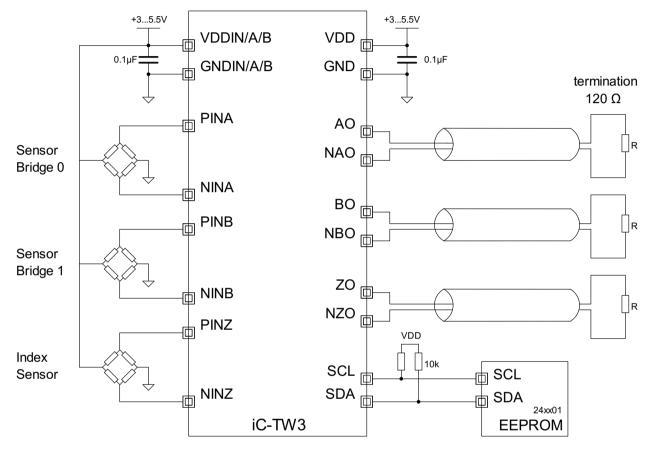

The general purpose sensor signal conditioner iC-TW3 provides highly accurate non contact trimming of three independent sine/cosine sensor signals. The differential output signals can be calibrated to 1 Vpp or to 2 Vpp, alternatively.

The internal or an external temperature sensor linked to the chip can influence the gain and offset correction by arbitrary temperature-dependent compensation parameters sourced from a look-up table.

For encoder applications an automatic gain and offset control compensates sensor offset voltages and stabilizes the output signal level.

The direct connection of sine/cosine encoders, MR sensor bridges or photosensor arrays is possible and supported by a selectable input impedance.

Rev B3, Page 3/26

#### **PACKAGING INFORMATION**

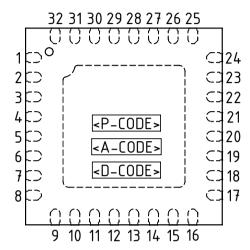

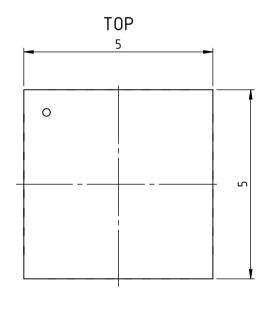

#### PIN CONFIGURATION QFN32 (5 mm x 5 mm)

(top view)

#### **PIN FUNCTIONS**

|    | Name                | Function                             |

|----|---------------------|--------------------------------------|

| 1  | PINZ                | Signal Input Z+                      |

| 2  | NINZ                | Signal Input Z-                      |

| 3  | TESTEN <sup>4</sup> | Test Mode Enable Input               |

| 4  | CLK <sup>5</sup>    | External Clock Input (optional)      |

| 5  | NZO                 | Signal Output Z-                     |

|    | ZO                  | Signal Output Z+                     |

| 7  | GNDB                | Driver Ground                        |

| 8  | VDDB                | +3+5.5 V Driver Supply Voltage       |

| 9  | NBO                 | Signal Output B-                     |

| 10 | ВО                  | Signal Output B+                     |

| 11 | GND                 | Digital Ground                       |

| 12 | SCL                 | I2C Interface, clock line            |

| 13 | SDA                 | I2C interface, data line             |

| 14 | VDD                 | +3+5.5 V Digital Supply Voltage      |

| 15 | GNDA                | Driver Ground                        |

| 16 | n.c. <sup>1</sup>   |                                      |

| 17 | AO                  | Signal Output A+                     |

| 18 | NAO                 | Signal Output A-                     |

| 19 | VDDA                | +3+5.5 V Driver Supply Voltage       |

| 20 | 1W                  | 1-Wire Interface, bidirectional port |

|    | NERR                | Error Message Output (active low)    |

|    | NRST                | External Reset Input (active low)    |

| 23 |                     | Coefficient Store Input (active low) |

| 24 |                     |                                      |

| 25 |                     | Signal Input A-                      |

|    | PINA                | Signal Input A+                      |

|    | KELVIN <sup>5</sup> | External Temperature Sensor Input    |

|    | GNDIN               | Input Ground                         |

|    | VDDIN               | +3+5.5 V Input Supply Voltage        |

|    | PINB                | Signal Input B+                      |

|    | NINB                | Signal Input B-                      |

| 32 | VC                  | 1.21 V Reference Voltage Output,     |

|    |                     | Reference Voltage Input (optional)   |

| TP | TP <sup>3</sup>     | Thermal Pad                          |

|    |                     |                                      |

IC top marking: <P-CODE> = product code, <A-CODE> = assembly code (subject to changes), <D-CODE> = date code (subject to changes);

<sup>&</sup>lt;sup>1</sup> Pin is not connected.

<sup>&</sup>lt;sup>2</sup> Pin NSTORE should be wired to VDD.

<sup>&</sup>lt;sup>3</sup> The Thermal Pad of the QFN package (bottom side) is to be connected to a ground plane on the PCB which must have GND potential.

<sup>&</sup>lt;sup>4</sup> Pin features an internal pull-down. Connect to GND if there is no need to enable chip test functions for verification.

<sup>&</sup>lt;sup>5</sup> Pin can remain open when not in use.

Rev B3, Page 4/26

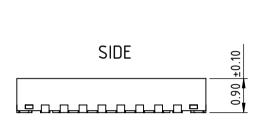

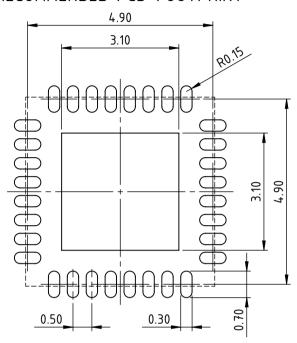

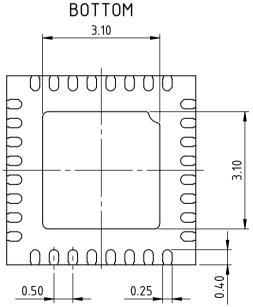

#### **PACKAGE DIMENSIONS**

#### RECOMMENDED PCB-FOOTPRINT

All dimensions given in mm. Tolerances of form and position according to JEDEC M0–220.

dra\_qfn32-5x5-3\_pack\_1, 10:1

Rev B3, Page 5/26

#### **ABSOLUTE MAXIMUM RATINGS**

These ratings do not imply operating conditions; functional operation is not guaranteed. Beyond these ratings device damage may occur.

| Item | Symbol | Parameter                                                       | Conditions                            |      |           | Unit |

|------|--------|-----------------------------------------------------------------|---------------------------------------|------|-----------|------|

| No.  | -      |                                                                 |                                       | Min. | Max.      |      |

| G001 | VDDx() | Voltage at VDD, VDDA, VDDB, VDDIN                               | referenced to GND, GNDA, GNDB, GNDIN  | -0.3 | 6.0       | V    |

| G002 | V()    | Voltage applied to any other pin                                | referenced to GND                     | -0.3 | VDD + 0.5 | V    |

| G003 | V()    | Voltage Difference VDDA, VDDB vs. VDD                           |                                       |      | 0.5       | V    |

| G004 | V()    | Voltage Difference VDDIN vs. VDD                                |                                       |      | 0.5       | V    |

| G005 | V()    | Voltage Difference GNDA, GNDB vs. GND                           |                                       |      | 0.5       | V    |

| G006 | V()    | Voltage Difference GNDIN vs. GND                                |                                       |      | 0.5       | V    |

| G007 | Vd     | ESD Susceptibility Of Signal Outputs: AO, NAO, BO, NBO, ZO, NZO | HBM, 100 pF discharged through 1.5 kΩ |      | 2         | kV   |

| G008 | Vd     | ESD Susceptibility (remaining pins)                             | HBM, 100 pF discharged through 1.5 kΩ |      | 2         | kV   |

| G009 | Ptot   | Permissible Power Dissipation                                   |                                       |      | 500       | mW   |

| G010 | Tj     | Junction Temperature                                            |                                       | -40  | 150       | °C   |

#### **THERMAL DATA**

| Item | Symbol | Parameter Conditions                |                                              |      |      |      | Unit |

|------|--------|-------------------------------------|----------------------------------------------|------|------|------|------|

| No.  |        |                                     |                                              | Min. | Тур. | Max. |      |

| T01  | Та     | Operating Ambient Temperature Range |                                              | -40  |      | 125  | °C   |

| T02  | Rthja  | ·                                   | surface mounted to PCB according to JEDEC 51 |      | 40   |      | K/W  |

| T03  | Ts     | Storage Temperature                 |                                              | -40  |      | 150  | °C   |

Rev B3, Page 6/26

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD, VDDA, VDDB, VDDIN = 3.0...5.5 V, Tj = -40...125 °C, reference point GND unless otherwise stated

| ltem<br>No. | Symbol      | Parameter                                                | Conditions                                                                                                              | Min.       | Тур.                | Max.        | Unit                    |

|-------------|-------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------|---------------------|-------------|-------------------------|

| Total       | Device      |                                                          |                                                                                                                         |            |                     |             |                         |

| 001         | VDDx        | Permissible Supply Voltage at VDD, VDDA, VDDB, VDDIN     |                                                                                                                         | 3.0        |                     | 5.5         | V                       |

| 002         | I(VDDx)     | Total Supply Current                                     | VDDx = 3.3 V<br>VDDx = 5.5 V                                                                                            |            |                     | 15<br>25    | mA<br>mA                |

| 003         | Vc()hi      | Clamp-Voltage hi at all pins                             | Vc()hi = V() - VDD; I() = 10 mA                                                                                         | 0.3        |                     | 1.4         | V                       |

| 004         | Vc()lo      | Clamp-Voltage lo at all pins                             | I() = -10 mA                                                                                                            | -1.2       |                     | -0.3        | V                       |

| Analo       | g Signal In | puts PINA, NINA, PINB, NINB, PIN                         | IZ, NINZ                                                                                                                |            |                     |             |                         |

| 101         | Vin()sig    | Permissible Input Voltage Range                          |                                                                                                                         | 1.4        |                     | VDD<br>-1.2 | V                       |

| 102         | Vin()os     | Input Offset Voltage                                     |                                                                                                                         |            | ±5                  | ±15         | mV                      |

| 103         | lin()       | Input Current                                            | ENSIGAB = 0, ENSIGZ = 0                                                                                                 | -35        |                     | 35          | nA                      |

| 104         | Rpu()       | Input Pull-Up Resistor                                   | ENSIGAB = 1, ENSIGZ = 1                                                                                                 | 2.0        | 2.5                 | 3           | MΩ                      |

| 105         | fg          | -3 dB Bandwidth                                          | PGA gain of 36 dB                                                                                                       | 1.2        |                     |             | MHz                     |

| 106         | CMRR        | Common Mode Rejection Ratio                              | fc < 1 MHz<br>fc < 1 kHz                                                                                                |            | 40<br>60            |             | dB<br>dB                |

| 107         | PSRR        | Power Supply Rejection Ratio                             | fc < 1 MHz<br>fc < 1 kHz                                                                                                |            | 40<br>60            |             | dB<br>dB                |

| 108         | en          | Input Voltage Noise                                      | f = 1 kHz<br>f = 100 Hz<br>f = 0.1 to 10 Hz                                                                             |            | 20 n<br>25 n<br>2 µ |             | V/√Hz<br>V/√Hz<br>V/√Hz |

| 109         | ∆DGAIN      | Dynamic Gain Step Width                                  |                                                                                                                         |            | 0.08                |             | dB                      |

| 110         | △DOFFS      | Dynamic Offset Step Width                                |                                                                                                                         |            | 2                   |             | mV                      |

| Temp        | erature Sen | sor and Analog Input KELVIN                              |                                                                                                                         |            |                     |             |                         |

| 201         | Tor         | Int. Temperature Sensor Operating Range                  | after calibration of ADC;                                                                                               | -50        |                     | 150         | °C                      |

| 202         | Tacc        | Device-To-Device Temp. Sensor Variation                  | after calibration of ADC,<br>Tj = -40 °C to 125 °C                                                                      |            | ± 10                |             | °C                      |

| 203         | Vin()low    | Temperature Input Voltage                                | CELSIUS(7:0) = 10<br>CELSIUS(7:0) = 245                                                                                 |            | 1.7<br>0.9          |             | V                       |

| 204         | lin()       | Input Current at KELVIN                                  | V(KELVIN) = 0 VDD                                                                                                       | -50        |                     | 50          | nA                      |

| 205         | T()lo       | Lo-Temperature ADC Reading, via Register CELSIUS(7:0)    | after calibration of ADC;<br>XCELSIUS = 0, internal sensor: Tj = -40 °C<br>XCELSIUS = 1, ext. sensor: V(KELVIN) = 1.7 V |            | 19<br>10            |             |                         |

| 206         | T()hi       | Hi-Temperature ADC Reading,<br>via Register CELSIUS(7:0) | after calibration of ADC;<br>XCELSIUS = 0, internal sensor: Tj = 125 °C<br>XCELSIUS = 1, ext. sensor: V(KELVIN) = 0.9 V |            | 224<br>245          |             |                         |

| Refer       | ence Voltag | e Input/Output VC                                        |                                                                                                                         |            |                     |             |                         |

| 301         | Vout(VC)    | Reference Voltage Output                                 | VEXT = 0; CL = 100 nF, I() = 0 mA                                                                                       | 1.10       | 1.21                | 1.35        | V                       |

| 302         | Vin(VC)     | Permissible Input Voltage Range at VC                    | VEXT = 1                                                                                                                | 0          |                     | 2.21        | V                       |

| 303         | lin(VC)     | Input Current at VC                                      | VEXT = 1                                                                                                                | -0.1       |                     | 1           | μA                      |

| Powe        | r-On Reset  | and Input NRST                                           |                                                                                                                         |            |                     |             |                         |

| 401         | VDDon       | Turn-On Threshold (power-on release)                     | increasing voltage at VDD                                                                                               |            |                     | 3.0         | V                       |

| 402         | VDDoff      | Turn-Off Threshold (power-down reset)                    | decreasing voltage at VDD                                                                                               |            | 2.6                 |             | V                       |

| 403         | Vt()hi      | Input Threshold Voltage hi                               | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %                                                                            | 1.5<br>3.3 |                     |             | V                       |

| 404         | Vt()lo      | Input Threshold Voltage lo                               | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %                                                                            |            |                     | 0.8<br>1.0  | V                       |

| 405         | lpu()       | Input Pull-Up Current                                    | V() = 0VDD - 1 V                                                                                                        |            |                     | -3          | μA                      |

| 406         | Vpu()       | Input Pull-Up Voltage                                    | Vpu() = VDD - V(), I() = -3 μA                                                                                          |            |                     | 700         | mV                      |

Rev B3, Page 7/26

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD, VDDA, VDDB, VDDIN = 3.0...5.5 V, Tj = -40...125 °C, reference point GND unless otherwise stated

| Item   | Symbol        | Parameter                                   | Conditions                                                               | B47        | I <b></b> |            | Unit       |

|--------|---------------|---------------------------------------------|--------------------------------------------------------------------------|------------|-----------|------------|------------|

| No.    |               | <u> </u>                                    |                                                                          | Min.       | Тур.      | Max.       |            |

|        | ator CLK, T   |                                             |                                                                          | 1          |           |            |            |

| 501    | Vt()hi        | Input Threshold Voltage hi                  | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %                             | 1.5<br>3.3 |           |            | V          |

| 502    | Vt()Io        | Input Threshold Voltage lo                  | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %                             |            |           | 0.8<br>1.0 | V          |

| 503    | lpd()         | Input Pull-Down Current                     | V() = 1 VVDD                                                             | 3          |           |            | μA         |

| 504    | Vpd()         | Input Pull-Down Voltage                     | I() = 3 μA                                                               |            |           | 700        | mV         |

| 505    | fosc          | Oscillator Frequency                        | TEST_CLK = 1, measured at NERR;<br>CLKDIV = 0 (low active)<br>CLKDIV = 1 |            |           | 2<br>4     | MHz<br>MHz |

| 506    | fin()         | Permissible External Clock Frequency at CLK |                                                                          |            |           | 4          | MHz        |

| 1-Wir  | e Interface 1 | W                                           |                                                                          |            |           |            |            |

| 601    | Vs()lo        | Saturation Voltage lo                       | I() = 1 mA                                                               |            |           | 300        | mV         |

| 602    | Isc()lo       | Short-Circuit Current lo                    |                                                                          | 2          |           |            | mA         |

| 603    | lpu()         | Input Pull-Up Current                       | V() = 0VDD - 1 V                                                         |            |           | -3         | μA         |

| 604    | Vpu()         | Input Pull-Up Voltage                       | Vpu() = VDD - V(), I() = -3 μA                                           |            |           | 700        | mV         |

| 605    | tr(), tf()    | Rise and Fall Time (10/90%)                 | VDD = 3.3 V, CL = 10 pF                                                  |            |           | 32         | ns         |

| 606    | Vt()hi        | Input Threshold Voltage hi                  | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %                             | 1.5<br>3.3 |           |            | V          |

| 607    | Vt()lo        | Input Threshold Voltage lo                  | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %                             |            |           | 0.8<br>1.0 | V          |

| I2C In | terface SDA   | , SCL                                       |                                                                          | "          |           |            |            |

| 701    | Vs()lo        | Saturation Voltage lo                       | I() = 1 mA                                                               |            |           | 400        | mV         |

| 702    | Isc()lo       | Short-Circuit Current lo                    | V() = 1VVDD                                                              | 3          |           |            | mA         |

| 703    | lpu()         | Pull-Up Current                             | V() = 0VDD - 1 V                                                         |            |           | -3         | μA         |

| 704    | Vpu()         | Input Pull-Up Voltage                       | Vpu() = VDD - V(), I() = -3 μA                                           |            |           | 700        | mV         |

| 705    | Vt()hi        | Input Threshold Voltage hi at SDA           | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %                             | 1.5<br>3.3 |           |            | V          |

| 706    | Vt()lo        | Input Threshold Voltage lo at SDA           | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %                             |            |           | 0.8<br>1.0 | V          |

| 707    | fclk()        | Write/Read Clock Frequency at SCL           | CLKDIV = 0                                                               |            | 100       |            | kHz        |

| 708    | tbusy()cfg    | Duration Of Startup Configuration           | CLKDIV = 0, 2 LUT blocks<br>CLKDIV = 0, 16 LUT blocks                    |            |           | 20<br>80   | ms<br>ms   |

| Digita | Output NE     | RR                                          |                                                                          | *          |           |            |            |

| 901    | Vs()lo        | Saturation Voltage lo                       | I() = 1 mA                                                               |            |           | 400        | mV         |

| 902    | Vs()hi        | Saturation Voltage hi                       | Vs()hi = VDD - V(); I() = -1 mA                                          |            |           | 400        | mV         |

| 903    | Isc()lo       | Short-Circuit Current lo                    |                                                                          | 3          |           |            | mA         |

| 904    | Isc()hi       | Short-Circuit Current hi                    |                                                                          |            |           | -2.5       | mA         |

Rev B3, Page 8/26

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD, VDDA, VDDB, VDDIN = 3.0...5.5 V, Tj = -40...125 °C, reference point GND unless otherwise stated

| Item   | Symbol         | Parameter                       | Conditions                                                                           |          |       |      | Unit         |

|--------|----------------|---------------------------------|--------------------------------------------------------------------------------------|----------|-------|------|--------------|

| No.    |                |                                 |                                                                                      | Min.     | Тур.  | Max. |              |

| Line D | river Outpu    | ts AO, NAO, BO, NBO, ZO, NZO    |                                                                                      |          |       |      |              |

| B01    | Vpk()max       | Permissible Output Amplitude    | VDD = 3 V, RL = $50 \Omega$ vs. VDD/2                                                |          |       | 550  | mV           |

| B02    | Vdc()          | Output DC Voltage               |                                                                                      |          | VDD/2 |      |              |

| B03    | △Vout()        | Output Voltage Load Dependency  | I() = 05 mA                                                                          |          |       | 50   | mV           |

| B04    | Isc()lo        | Short-Circuit Current lo        | pin shorten to VDD/2                                                                 | 12       |       | 50   | mA           |

| B05    | Isc()hi        | Short-Circuit Current hi        | pin shorten to VDD/2                                                                 | -50      |       | -12  | mA           |

| B06    | Isc()          | Output Current Limitation hi/lo | V() = 0VDD                                                                           |          | 40    | 50   | mA           |

| B07    | SR()hi, lo     | Slew Rate hi/lo                 | CL() = 5 nF<br>CL() = 50 pF                                                          | 3<br>4   |       |      | V/µs<br>V/µs |

| B08    | t <sub>S</sub> | Settling Time                   | CL() = 5 nF, to 0.1% of final value                                                  |          |       | 1    | μs           |

| B09    | dbVlin         | Output Linearity                | 100 kHz sine and diff. 1 Vpp output voltage; RL() > 1 k $\Omega$ RL() = 120 $\Omega$ | 80<br>60 |       |      | dB<br>dB     |

| B10    | CLmax          | Maximum Capacitive Output Load  | no sustained oscillation                                                             |          | 100   |      | nF           |

Rev B3, Page 9/26

#### **PROGRAMMING**

PDZ:

Power down control for channel Z

POLARITYZ: Channel Z polarity select

| Register Map         | Page 11                                           | Automatic Co<br>VEXT:<br>DYNAMIC:       | mpensation                                                              |

|----------------------|---------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------|

|                      | CE Page 12 EEPROM Checksum                        | FREQ:<br>GENTLE:                        | Automatic adaption frequency Automatic compensation update rate         |

| 1-Wire Interfa       | <b>ce</b> Page 13                                 | Temperature S<br>XCELSIUS:<br>FCELSIUS: | Sensing Page 20 Temperature sensor select Fine temperature offset value |

| A/R Signal Pa        | th Page 15                                        | CCELSIUS:                               | Coarse temperature offset value                                         |

| SINGLEIN:            | Single ended input functionality                  | CELSIUS:                                | Current temperature value                                               |

| ENSIGAB:             | Input signal error detection control              | 00.00.                                  |                                                                         |

| CGAINA/B:            | Coarse gain select for channel A/B                | Error Condition                         | ons Page 21                                                             |

| COFSA/B:             | Coarse offset select for channel A/B              | ERR SIG:                                | Signal unconnected alarm                                                |

| DGAINA/B:            | Dynamic gain on channel A/B                       | ERR_TEMP:                               | Temperature alarm                                                       |

| DOFSA/B:             | Dynamic offset on channel A/B                     | ERR_EE:                                 | EEPROM error condition                                                  |

| OGAIN:               | Output amplifier gain select on channel           | _                                       |                                                                         |

|                      | A/B                                               | Temperature (                           | Compensation Page 22                                                    |

| FILTER:              | Signal path filter select                         | TEMP:                                   | Temperature compensation control                                        |

| PDA/B:               | Power down control for channel A/B                |                                         |                                                                         |

|                      |                                                   | Test Modes                              | Page 23                                                                 |

| <b>Z Signal Path</b> | (Index) Page 17                                   | PD_CELSIUS                              | : Power down control for internal tem-                                  |

| SINGLEZ:             | Single ended input functionality for in-          |                                         | perature sensor                                                         |

|                      | dex channel Z                                     | TEST_CLK:                               | Internal test clock oscillator control                                  |

| MODEZ:               | Channel Z output mode select                      | CLKDIV:                                 | Internal clock divider select                                           |

| BYPASSZ:             | Channel Z comparator bypass control               |                                         |                                                                         |

| GAINZ:               | Gain select for channel Z                         | Typical Applic                          | cations Page 24                                                         |

| OFSZ:                | Offset select for channel Z                       |                                         |                                                                         |

| OGAINZ:              | Output amplifier gain select on channel Z         |                                         |                                                                         |

| ENSIGZ:              | Input signal error detection control on channel 7 |                                         |                                                                         |

Rev B3, Page 10/26

|              | TER MAP        | Bit 6                 | D:4 F                 | Bit 4                 | D:t 3               | D:4 0               | Dit 4                 | D:t O                   |

|--------------|----------------|-----------------------|-----------------------|-----------------------|---------------------|---------------------|-----------------------|-------------------------|

| Addr         | Bit 7          |                       | Bit 5                 | Bit 4                 | Bit 3               | Bit 2               | Bit 1                 | Bit 0                   |

|              | uration Regist | ers '                 |                       |                       |                     |                     |                       |                         |

| 0x00         |                |                       | 1                     | 1                     | ice ID[7:0]         |                     | T                     |                         |

| 0x01         |                | IN[1:0]               | SINGLEIN              | FRE                   |                     | GENTLE              | DYNAMIC               | TEMP                    |

| 0x02         | VEXT           | XCELSIUS              |                       | NZ[1:0]               | MODEZ               | BYPASSZ             | SINGLEINZ             | POLARITYZ               |

| 0x03         | ERR_SIG        | ERR_TEMP              | ERR_EE                |                       | TALARM[2:0]         | т.                  | ENSIGZ                | ENSIGAB                 |

| 0x04         | EN_NSTORE 2    |                       |                       | FILTE                 | R[1:0]              | PDZ                 | PDB                   | PDA                     |

| 0x05         |                | CCELS                 | IUS[3:0]              |                       |                     |                     | IUS[3:0]              |                         |

| 0x06         | GAINZ[2]       |                       |                       |                       | OFS.                | Z[5:0]              |                       |                         |

| 0x07         | GAIN           | IZ[1:0]               |                       | CGAINB[2:0]           |                     |                     | CGAINA[2:0]           |                         |

| 80x0         |                |                       |                       | COFS                  | A[7:0]              |                     |                       |                         |

| 0x09         |                |                       |                       |                       | B[7:0]              |                     |                       |                         |

| 0x0A         |                |                       |                       | DGAIN                 | NA[7:0]             |                     |                       |                         |

| 0x0B         |                |                       |                       | DGAIN                 | NB[7:0]             |                     |                       |                         |

| 0x0C         |                |                       |                       |                       | SA[7:0]             |                     |                       |                         |

| 0x0D         |                |                       |                       | DOFS                  | B[7:0]              |                     |                       |                         |

| 0x0E         | 0              | 0                     | VC[                   | 1:0] <sup>2</sup>     | CLKSLOW 2           | CLKDIV <sup>2</sup> | TEST_CLK <sup>2</sup> | PD_CELSIUS <sup>2</sup> |

| 0x0F         |                |                       |                       | Internal Che          | ecksum(7:0)         |                     |                       |                         |

| 0x10         | 0              | TEST_ADC <sup>2</sup> | TEST_VGA <sup>2</sup> | TEST_PGA <sup>2</sup> | VTEST1 <sup>2</sup> | VTEST0 <sup>2</sup> | PD_BG <sup>2</sup>    | TEST_BG <sup>2</sup>    |

| 0x11         |                |                       |                       |                       |                     |                     |                       |                         |

| 0x12         |                |                       |                       | CELSI                 | US[7:0]             |                     | •                     | •                       |

| 0x13         |                |                       |                       |                       |                     |                     |                       |                         |

| Interna      | l State Machin | e Registers           |                       |                       |                     |                     |                       |                         |

| 0x14         |                |                       |                       | INTERN                | IAL USE             |                     |                       |                         |

| 0x15         |                |                       |                       | INTERN                | IAL USE             |                     |                       |                         |

| 0x16         |                |                       |                       | INTERN                | IAL USE             |                     |                       |                         |

| 0x17         |                |                       |                       | INTERN                | IAL USE             |                     |                       |                         |

| 0x18         |                |                       |                       | INTERN                | IAL USE             |                     |                       |                         |

| 0x19         |                |                       |                       | INTERN                | IAL USE             |                     |                       |                         |

| 0x1A         |                |                       |                       | INTERN                | IAL USE             |                     |                       |                         |

| 0x1B         |                |                       |                       | INTERN                | IAL USE             |                     |                       |                         |

| 0x1C         |                |                       |                       | INTERN                | IAL USE             |                     |                       |                         |

| 0x1D         |                |                       |                       |                       | IAL USE             |                     |                       |                         |

| 0x1E         |                |                       |                       | INTERN                | IAL USE             |                     |                       |                         |

| 0x1F         |                |                       |                       |                       | IAL USE             |                     |                       |                         |

| 0x20         |                |                       |                       |                       | IAL USE             |                     |                       |                         |

| 0x21         |                |                       |                       | INTERN                | IAL USE             |                     |                       |                         |

| 0x22         |                |                       |                       |                       | IAL USE             |                     |                       |                         |

| 0x23         |                |                       |                       |                       | IAL USE             |                     |                       |                         |

| 0x24         | 1              |                       |                       |                       | IAL USE             |                     |                       |                         |

| 0x25         | 1              |                       |                       |                       | IAL USE             |                     |                       |                         |

| 0x26         | +              |                       |                       |                       | IAL USE             |                     |                       |                         |

| 0x27         |                |                       |                       |                       | IAL USE             |                     |                       |                         |

|              | ral Registers  |                       |                       |                       |                     |                     |                       |                         |

| 0x40         | Tai itegisters |                       |                       | CEI SILIS             | RAW[7:0]            |                     |                       |                         |

| 0x40<br>0x41 | +              |                       |                       | CHANNEL               | OFS_P               | OFS_N               | GAIN_P                | GAIN_N                  |

| 0x41<br>0x42 |                |                       | EE_ERR                | XERR_OUT              | 10UTPUT             | 1INPUT              | XSTORE                | SIG_VALID               |

| UX4Z         |                |                       | CC_EKK                | VEKK_OOI              | 1001901             | HINFUI              | ASTURE                | SIG_VALID               |

Rev B3, Page 11/26

| REGIST | REGISTER MAP                                                         |                   |               |               |              |            |                 |       |  |

|--------|----------------------------------------------------------------------|-------------------|---------------|---------------|--------------|------------|-----------------|-------|--|

| Addr   | Bit 7                                                                | Bit 6             | Bit 5         | Bit 4         | Bit 3        | Bit 2      | Bit 1           | Bit 0 |  |

| 0x43   |                                                                      |                   | EE_IRQ        |               |              | 1INPUT_IRQ | XS-<br>TORE_IRQ |       |  |

| Notes  | <sup>1</sup> Only the configuration registers are user programmable. |                   |               |               |              |            |                 |       |  |

|        | <sup>2</sup> Register b                                              | it for IC test of | only; must be | kept on 0 for | r normal ope | ration.    |                 |       |  |

Table 1: Register layout

Rev B3, Page 12/26

#### **12C INTERFACE**

#### Startup

An external I<sup>2</sup>C 1-kbit EEPROM (e.g. 24xx01 family) is used to store configuration parameters permanently. On power-up and after reset is released iC-TW3 accesses the external EEPROM and reads its device configuration according to Table 3.

#### **EEPROM Checksum**

The checksum at address 0x0F contains the 8-bit sum of registers 0x01 to 0x0E plus the 8-bit sum of all LUT bytes up to and including the final block with its breakpoint set to 255.

On startup iC-TW3 calculates the expected checksum and compares it with the value stored at EEPROM address 0x0F. If computed and stored address match normal operation begins. Otherwise, iC-TW3 asserts an error condition and pin NERR is pulled low.

It is the user's responsibility to store the correct checksum in the EEPROM during production programming.

| CHECKSUM | /I(7:0) | Addr. 0x0F;   | bit 7:0   | R/W              |

|----------|---------|---------------|-----------|------------------|

| Code     | Functi  | on            |           |                  |

|          | Check   | sum of EEPR   | OM conte  | ents:            |

|          | over 0  | x01 to 0x0E a | nd 0x10 t | o 0x1B (minimum) |

|          | over 0  | x01 to 0x0E a | nd 0x10 t | o 0x6F (maximum) |

Table 2: Checksum

**Note**: As the checksum includes the LUT, breakpoint 255 must be assigned to the final block.

#### **EEPROM Register Map**

The 14 bytes of device configuration data are followed by a minimum of 2 to a maximum of 16 lock-up-table blocks (LUT). The LUT block size is 6 bytes each and the final block is indicated by its breakpoint value of 255.

Thus, a minimum of 28 bytes are read with 2 active LUT blocks and 112 bytes are read with 16 active LUT blocks during the configuration phase.

The last LUT block ist indicated by a breakpoint value of 255. Further descriptions on LUTs are given in section "Temperature Compensation" on page 22.

Note that the EEPROM address space maps to the 1-wire address 128. Accessing EEPROM address 0 is therefore equivalent to accessing memory location 128 via the 1-wire interface (see page 13).

| EEPROM  | Description           | Corresponding          |

|---------|-----------------------|------------------------|

| Address | 1                     | Configuration Register |

| 0x00    | <reserved></reserved> | -                      |

| 0x01    | Config. 1             | 0x01                   |

| 0x02    | Config. 2             | 0x02                   |

| 0x03    | Config. 3             | 0x03                   |

| 0x04    | Config. 4             | 0x04                   |

| 0x05    | Temp. Sensing         | 0x05                   |

| 0x06    | Config. Index         | 0x06                   |

| 0x07    | Coarse Gain           | 0x07                   |

| 0x08    | COFSA                 | 0x08                   |

| 0x09    | COFSB                 | 0x09                   |

| 0x0A    | DGAINA                | 0x0A                   |

| 0x0B    | DGAINB                | 0x0B                   |

| 0x0C    | DOFSA                 | 0x0C                   |

| 0x0D    | DOFSB                 | 0x0D                   |

| 0x0E    | Test 1                | 0x0E                   |

| 0x0F    | CHECKSUM              | 0x0F                   |

| EEPROM  | Description           | LUT Block Number       |

| Address |                       |                        |

| 0x10    | Breakpoint 0          | 0                      |

| 0x11    | GAINA                 | 0                      |

| 0x12    | GAINB                 | 0                      |

| 0x13    | OFSA                  | 0                      |

| 0x14    | OFSB                  | 0                      |

| 0x15    | OFSZ                  | 0                      |

| 0x16    | Breakpoint 1 (255)    | 1                      |

| 0x17    | GAINA                 | 1                      |

| 0x18    | GAINB                 | 1                      |

| 0x19    | OFSA                  | 1                      |

| 0x1A    | OFSB                  | 1                      |

| 0x1B    | OFSZ                  | 1                      |

|         |                       |                        |

| -       |                       |                        |

| •       |                       | •                      |

| 0x6A    | Breakpoint 255        | 15                     |

| 0x6B    | GAINA                 | 15                     |

| 0x6C    | GAINB                 | 15                     |

| 0x6D    | OFSA                  | 15                     |

| 0x6E    | OFSB                  | 15                     |

| 0x6F    | OFSZ                  | 15                     |

Table 3: EEPROM register map

Rev B3, Page 13/26

#### 1-WIRE INTERFACE

The 1-wire interface provides read and write access to the register bank and to the external EEPROM. When read access is not required an infrared phototransistor can be directly connected to the pin in order to build a cost effective wireless write-only port for in-field or production programming.

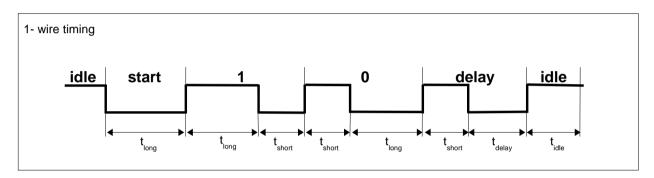

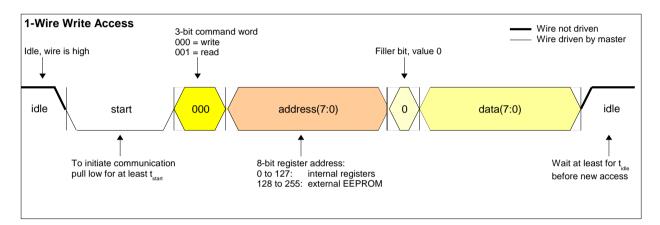

The communication bit stream is pulse-width modulated (PWM) as shown in Figure 1. A zero-bit is encoded as a

short high followed by a long low. A one-bit is encoded as a long high followed by a short low.

The modulated signal is independent of the receiver or the transmitted clock frequency. Since iC-TW3 uses a free-running oscillator it is important to implement a robust, frequency insensitive protocol.

Figure 1: Pulse width modulation bit stream

| Parameter          | Description                                                                                                   | min                        | max                       |

|--------------------|---------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------|

| t <sub>start</sub> | Low time start condition (Master only)                                                                        | 1 ms                       |                           |

| t <sub>long</sub>  | Unit time long (Master and iC-TW3)                                                                            | t <sub>short</sub> + 10 μs | 400 µs                    |

| t <sub>short</sub> | Unit time short (Master and iC-TW3)                                                                           | 35 µs                      | t <sub>long</sub> - 10 μs |

| t <sub>delay</sub> | Delay on register read (iC-TW3 only)                                                                          | 35 µs                      |                           |

| t <sub>idle</sub>  | Interface idle before next access Access was write to external EEPROM Access was not write to external EEPROM | 8 ms<br>3 ms               |                           |

Table 4: 1-Wire interface timing

Rev B3, Page 14/26

#### Addressing

The EEPROM address 0x00 maps to the 1-wire address 128. Accessing EEPROM address 0 is therefore equivalent to accessing memory location 128 through the 1-wire interface. All other 1-wire addresses are thus determined by adding 128 to the EEPROM address of interest.

#### **Write Sequence**

Figure 2 describes the write sequence of the 1-wire interface. On an idle wire, a write sequence is initiated

by generating a start condition followed by the write command (000) and by the address and register data.

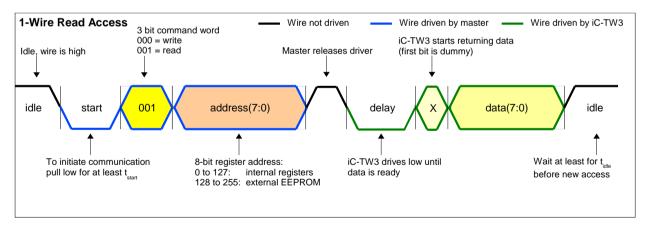

#### Read Sequence

A read sequence is depicted in Figure 3. After the start condition the read command (001) is followed by the register address. The master then releases the wire and iC-TW3 begins to pull low while internally accessing the data. When the data is ready it is produced while following the same PWM rules valid for the master.

Figure 2: Register write sequence

Figure 3: Register read sequence

Rev B3, Page 15/26

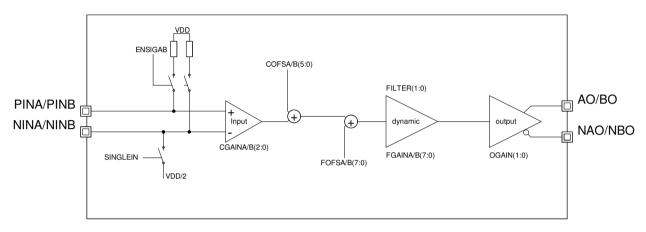

#### A/B SIGNAL PATH

iC-TW3 incorporates two analog gain paths called channel A and B, respectively. Gain and offset of both paths are independently controlled and temperature compen-

sated. Figure 4 depicts a diagram of a single signal path, Table 5 below summarizes gain and offset characteristics.

Figure 4: The A/B signal path

|                             | Input Amplifier                                                     | Dynamic Amplifier                | Output Amplifier  | Composite                        |

|-----------------------------|---------------------------------------------------------------------|----------------------------------|-------------------|----------------------------------|

| Gain range                  | 036 dB                                                              | -218.4 dB                        | -3 dB, 0 dB, 6 dB | -560 dB                          |

| Gain step                   | 6.0 dB                                                              | 0.08 dB                          |                   |                                  |

| Offset range input referred | ±1.24 V<br>gain <sub>input</sub>                                    | ±0.25 V<br>gain <sub>input</sub> |                   | ±1.49 V<br>gain <sub>input</sub> |

| Offset step input referred  | 40 mV<br>gain <sub>input</sub>                                      | 2 mV<br>gain <sub>input</sub>    |                   |                                  |

|                             | $gain_{input} = 10^{\frac{gain\_of\_input\_amplifier\_in\_dB}{20}}$ |                                  |                   |                                  |

Table 5: Overview of gain and offset characteristics

#### Single ended signals

Single ended input functionality is provided by connecting the negative input terminal (pins NINA and NINB) to an internally generated voltage of  $V_{DD}/2$ . This is enabled by setting the control bit *SINGLEIN* to 1. Alternatively, an externally generated reference voltage may be applied to the negative input terminals.

| SINGLEIN | Addr. 0x01; bit 5                         | R/W |

|----------|-------------------------------------------|-----|

| Code     | Function                                  |     |

| 0        | A and B inputs are differential (default) |     |

| 1        | A and B inputs are single ended           |     |

Table 6: Single ended input functionality

#### Input error detection

Weak input pull-up resistors are enabled by setting control bit *ENSIGAB* to 1. The resistors are at minimum  $2.0\,\mathrm{M}\Omega$ . When driving the input with a high impedance source it might be necessary to disable the pull-up resistors to avoid excessive signal distortion. The pull-up resistors are used to sense floating or damaged sen-

sor connections. Any input terminal left unconnected is pulled to  $V_{\text{DD}}$  and triggers a sensor error condition  $err\_sig$ .

| ENSIGAB | Addr. 0x03; bit 0                                               | R/W    |

|---------|-----------------------------------------------------------------|--------|

| Code    | Function                                                        |        |

| 0       | Pull-up resistors disconnected and error rep disabled (default) | orting |

| 1       | Pull-up resistors and error reporting active of inputs          | on A/B |

Table 7: Input signal error detection control

#### Gain and offset

Registers *CGAINA(2:0)* and *CGAINB(2:0)* are used to set the coarse gain. Coarse gain is static and it is not changed by the temperature or automatic compensation algorithm.

The highest legal value for *CGAINA(2:0)* and *CGAINB(2:0)* is 6. Equivalently registers *COFSA(5:0)* and *COFSB(5:0)* are used to control the static offset of the input signal. Note that *COFSA(5:0)* and

Rev B3, Page 16/26

COFSB(5:0) are in 2's complement format and their value range is limited from -31 to +31.

| CGAINA(2:0 | Addr. 0x07;         | bit 2:0 | R/W |

|------------|---------------------|---------|-----|

| CGAINB(2:0 | Addr. 0x07;         | bit 5:3 | R/W |

| Code       | gain = cgain x 6 dB |         |     |

| 0x00       | 0 dB (default)      |         |     |

| 0x01       | 6 dB                |         |     |

| ***        |                     |         |     |

| 0x06       | 36 dB               |         |     |

Table 8: Coarse gain select for channel A/B

| COFSA(7:0) | ) Addr. 0x08; bit 7:  | 0 R/W                         |

|------------|-----------------------|-------------------------------|

| COFSB(7:0) | Addr. 0x09; bit 7:    | 0 R/W                         |

| Code 2'K   | Code 5:0, and decimal | $offset = cofs \times 40  mV$ |

| 0xE1       | 0x21, -31             | -1240 mV                      |

|            |                       |                               |

| 0xFF       | 0x3F, -1              | -40 mV                        |

| 0x00       | 0x00, 0               | 0 mV (default)                |

| 0x01       | 0x01, +1              | 40 mV                         |

|            |                       |                               |

| 0x1F       | 0x1F, +31             | 1240 mV                       |

Table 9: Coarse offset select for channel A/B

| DGAINA(7: | <b>0)</b> Addr. 0x0A; bit 7:0 R/W | / |

|-----------|-----------------------------------|---|

| DGAINB(7: | 0) Addr. 0x0B; bit 7:0 R/W        | / |

| Code      | gain = dgain x 0.08 dB - 2 dB     |   |

| 0x00      | -2 dB (default)                   |   |

|           |                                   |   |

| 0x19      | 0 dB                              |   |

| 0x1A      | 0.08 dB                           |   |

|           |                                   |   |

| 0xFF      | 18.4 dB                           |   |

Table 10: Dynamic gain select for channel A/B

| DOESA/7:0) | Addr. 0x0C;                  | hit 7:0 | R/W  |

|------------|------------------------------|---------|------|

| DOFSA(7:0) | Addi. UXUC,                  | DIL 7.U | R/VV |

| DOFSB(7:0) | Addr. 0x0D;                  | bit 7:0 | R/W  |

| Code       | $offset = cofs \ x \ 2 \ mV$ |         |      |

| 0x81       | -254 mV                      |         |      |

|            |                              |         |      |

| 0xFF       | -2 mV                        |         |      |

| 0x00       | 0 mV (default)               |         |      |

| 0x01       | 2 mV                         |         |      |

|            |                              |         |      |

| 0x7F       | 254 mV                       |         |      |

Table 11: Dynamic offset select for channel A/B

Value FGAINA/B and FOFSA/B are fine gain and offset control respectively. They are calculated dynamically according to the temperature compensation algorithm. In case temperature compensation is not enabled the values of FGAINA/B and FOFSA/B are equal to the register values in DGAINA/B(7:0) and DOFSA/B(7:0). Refer to chapter "Temperature Compensation" on page 22 for a detailed explanation of fine gain and fine offset calculations. DGAINA/B(7:0) and DOFSA/B(7:0) can be programmed to a fixed value or it is automatically updated when dynamic adaption is enabled.

#### **Output driver**

The output amplifier is capable of driving a  $100\,\Omega$  differential load and is stable with capacitive loads of up to  $100\,\text{nF}$ . Control register OGAIN(1:0) is used to select the output amplifier gain. A gain of -3 dB is useful to accommodate input signals larger than 1 V and gain of +6 dB will provide a 1 Vpp single-ended output. Note that the selected output amplifier gain will influence the automatic gain compensation. Refer to section "Automatic Compensation" on page 19 for details.

| OGAIN(1:0) | Addr. 0x01; bit 7:6 | R/W |

|------------|---------------------|-----|

| Code       | Function            |     |

| 0x00       | 0 dB (default)      |     |

| 0x01       | Reserved            |     |

| 0x02       | +6 dB               |     |

| 0x03       | -3 dB               |     |

Table 12: Output amplifier gain on channel A/B

A programmable 1<sup>st</sup>-order low-pass filter can be enabled to limit the path bandwidth. The filter cut-off frequency can be set via the *FILTER*(1:0) register.

| FILTER(1:0) | Addr. 0x04; bit 4:3 | R/W |

|-------------|---------------------|-----|

| Code        | Function            |     |

| 0x00        | 1 MHz (default)     |     |

| 0x01        | 500 kHz             |     |

| 0x02        | 200 kHz             |     |

| 0x03        | reserved            |     |

Table 13: Signal path filter

In order to save power the complete signal path can be disabled using the control bits *PDA* and *PDB* respectively. When disabled the outputs are high impedance. The dynamic adaption should be disabled when either channel A or B is disabled.

| PDA  | Addr. 0x04; bit 0                | R/W |

|------|----------------------------------|-----|

| PDB  | Addr. 0x04; bit 1                | R/W |

| Code | Function                         |     |

| 0    | Channel A/B is enabled (default) |     |

| 1    | Channel A/B is powered down      |     |

Table 14: Power down control on channel A/B

Rev B3, Page 17/26

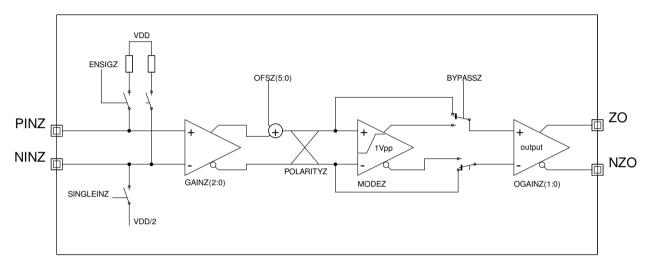

#### **Z SIGNAL PATH (INDEX)**

A third analog path is used for index signal processing frequently found in encoder applications. Refer to Figure 5 for an overview. An input amplifier with a gain range of 0 to 36 dB is used to amplify the index signal to an intermediate level. The input amplifier employs

output referred offset correction. This is used to eliminate inherent amplifier offset as well as sensor offset. Additionally, the same offset correction is used to skew the comparator shift point to a desired level. The offset correction is temperature compensated with a LUT.

Figure 5: The Z signal path

|                             | Input Amplifier                                                     | Output Amplifier                 | Composite |

|-----------------------------|---------------------------------------------------------------------|----------------------------------|-----------|

| Gain range                  | 036 dB                                                              | -3 dB, 0 dB, 6 dB                | -342 dB   |

| Gain step                   | 6 dB                                                                |                                  |           |

| Offset range input referred | ±1.86 V<br>gain <sub>input</sub>                                    | ±1.86 V<br>gain <sub>input</sub> |           |

| Offset step input referred  | 60 mV<br>gain <sub>input</sub>                                      |                                  |           |

|                             | gain <sub>input</sub> = 10 <sup>gain_of_input_amplifier_in_dB</sup> |                                  |           |

Table 15: Gain and offset characteristics for channel Z

A single ended input referenced to  $V_{DD}/2$  is provided by setting bit SINGLEINZ of register 0x02. Alternatively, pin NINZ can be biased with an external voltage.

| SINGLEINZ | Addr. 0x02; bit 1                         | R/W |

|-----------|-------------------------------------------|-----|

| Code      | Function                                  |     |

| 0         | Channel Z input is differential (default) |     |

| 1         | Channel Z is single ended                 |     |

Table 16: Single ended input functionality

A zero-crossing comparator generates a  $1.0\,V_{peak-peak}$  output signal or a rail-to-rail signal depending on control bit MODEZ. The comparator can be bypassed which allows using the Z Path as a regular amplifier path. Bypassing can be toggled via bit BYPASSZ of register 0x02.

| MODEZ | Addr. 0x02; bit 3                                     | R/W |

|-------|-------------------------------------------------------|-----|

| Code  | Function                                              |     |

| 0     | 1 Vpp out (default)                                   |     |

| 1     | Rail-to-rail output (requires OGAINZ(1:0) set to 0x2) |     |

Table 17: Channel Z output mode select

| BYPASSZ | Addr. 0x02; bit 2               | R/W |

|---------|---------------------------------|-----|

| Code    | Function                        |     |

| 0       | Comparator is enabled (default) |     |

| 1       | Comparator is bypassed          |     |

Table 18: Channel Z comparator bypass

Rev B3, Page 18/26

#### Gain and offset

Gain and offset selections on channel Z are made available by providing control bits *GAINZ(2:0)* and *OFSZ(5:0)*. Note that the maximum value for gain on channel Z is 6 which corresponds to a total gain of 36 dB.

*GAINZ(2:0)* is split up amongst register 0x06 which holds the MSB and register 0x07 holding the other two bits. *OFSZ(5:0)* is the correction value to the output of the input amplifier and is interpreted as 2's complement. The input referred offset is therefore gain dependent.

The output gain on channel Z can be set via control bits OGAINZ(1:0). For more details again refer to section "A/B PATH" on page 15.

| GAINZ(2:0) | Addr. 0x06;         | bit 7   | R/W |

|------------|---------------------|---------|-----|

|            | Addr. 0x07;         | bit 1:0 |     |

| Code       | gain = gainz x 6 dB |         |     |

| 0x00       | 0 dB (default)      |         |     |

| 0x01       | 6 dB                |         |     |

|            |                     |         |     |

| 0x06       | 36 dB               |         |     |

Table 19: Gain select for channel Z

| OFSZ(5:0) | Addr. 0x06; | bit 5: | 0 R/W                         |

|-----------|-------------|--------|-------------------------------|

| Code 2'K  | Decimal     |        | $offset = cofs \times 60  mV$ |

| 0x21      | -31         |        | -1860 mV                      |

|           |             |        |                               |

| 0x3F      | -1          |        | -60 mV                        |

| 0x00      | 0           |        | 0 mV (default)                |

| 0x01      | +1          |        | 60 mV                         |

|           |             |        |                               |

| 0x1F      | +31         |        | 1860 mV                       |

Table 20: Offset select for channel Z

| OGAINZ(1:0 | O) Addr. 0x02; bit 5:4 | R/W |

|------------|------------------------|-----|

| Code       | Function               |     |

| 0x00       | 0 dB (default)         |     |

| 0x01       | Reserved               |     |

| 0x02       | +6 dB                  |     |

| 0x03       | -3 dB                  |     |

Table 21: Output amplifier gain on channel Z

#### Input error detection

Pull-up resistor and error detection on channel Z can be controlled by bit *ENSIGZ* of register 0x03, disabling of the complete Z path can be achieved by setting bit *PDZ* of register 0x04 to 1. For more detailed information on pull-up and power control refer to section "A/B PATH" on page 15 as the behaviour of index path and signal path equal regarding these matters.

| ENSIGZ | Addr. 0x03; bit 1                                               | R/W           |

|--------|-----------------------------------------------------------------|---------------|

| Code   | Function                                                        |               |

| 0      | Pull-up resistors disconnected and error rep disabled (default) | orting        |

| 1      | Pull-up resistors and error reporting active of                 | on <i>inZ</i> |

Table 22: Input signal error detection control

| PDZ  | Addr. 0x04; bit 2              | R/W |

|------|--------------------------------|-----|

| Code | Function                       |     |

| 0    | Channel Z is enabled (default) |     |

| 1    | Channel Z is powered down      |     |

Table 23: Power-down control on channel Z

#### Polarity of channel Z

Furthermore, the polarity on channel Z can be inverted by setting or not setting bit *POLARITYZ*.

| POLARITYZ | Addr. 0x02; bit 0                       | R/W |

|-----------|-----------------------------------------|-----|

| Code      | Function                                |     |

| 0         | Channel Z has normal polarity (default) |     |

| 1         | Channel Z has inverted polarity         |     |

Table 24: Channel Z polarity select

Rev B3, Page 19/26

#### **AUTOMATIC COMPENSATION**

Automatic gain and offset correction is available for dual sensor bridges that are 90° out of phase. These types of sensors are used for encoder applications.

Automatic compensation removes any sensor offset and sets the gain to achieve a fixed output voltage. The target output voltage depends on the output gain *OGAIN(1:0)* as well as on the control bit *VEXT*. When using an external reference voltage, the appropriate voltage must be applied to pin VC.

| VEXT | Addr. 0x02; bit 7                                                                          | R/W           |

|------|--------------------------------------------------------------------------------------------|---------------|

| Code | Function                                                                                   |               |

| 0    | Internally generated 1 V or 2 V is used as out target voltage, depending on register OGAIN | put<br>(1:0). |

| 1    | Voltage applied to pin VC defines target outp voltage (see Table 26).                      | ut            |

Table 25: Target voltage selection

| OGAIN(1:0) | Output Gain | VEXT | Target Output<br>Voltage V <sub>ppdiff</sub> |

|------------|-------------|------|----------------------------------------------|

| 00         | 0 dB        | 0    | 1 V                                          |

| 01         | reserved    | 0    |                                              |

| 10         | 6 dB        | 0    | 2V                                           |

| 11         | -3 dB       | 0    | 1 V                                          |

| 00         | 0 dB        | 1    | 2.21 V - VC                                  |

| 01         | reserved    | 1    |                                              |

| 10         | 6 dB        | 1    | (2.21 V - VC) x 2                            |

| 11         | -3 dB       | 1    | 2.21 V - VC                                  |

Table 26: Target output voltages

Automatic compensation is enabled by setting control bit *DYNAMIC* of register 0x01 to 1. If enabled, it will constantly alter register *DOFSA/B* and *DGAINA/B* to maintain zero offset and the target output amplitude. Control bits *FREQ(1:0)* of register 0x01 are used to limit the tracking rate. If the input frequency increases above the limit tracking will stop. Normally, it is not required to limit the tracking frequency although it can be useful for certain bandwidth limited sensors.

| DYNAMIC | Addr. 0x01; bit 1              | R/W |

|---------|--------------------------------|-----|

| Code    | Function                       |     |

| 0       | Automatic function is disabled |     |

| 1       | Automatic function is enabled  |     |

Table 27: Automatic compensation enable

Note that setting FREQ(1:0) to other values than 0 does not affect the signal bandwidth of the amplifier. It merely limits the rate of automatic adaption.

| FREQ(1:0) | Addr. 0x01; bit 4:3         | R/W |

|-----------|-----------------------------|-----|

| Code      | Function                    |     |

| 00        | No tracking limit (default) |     |

| 01        | 200 kHz                     |     |

| 10        | 20 kHz                      |     |

| 11        | 2 kHz                       |     |

Table 28: Automatic compensation adaption rate

In normal operation the compensation algorithm will adjust both gain and offset simultaneously in order to achieve fast convergence. If control bit *GENTLE* of register 0x01 is set, gain and offset registers are updated alternately. This reduces output jumpiness at the expense of slower convergence.

| GENTLE | Addr. 0x01; bit 2                          | R/W |

|--------|--------------------------------------------|-----|

| Code   | Function                                   |     |

| 0      | Gain and offset are updated simultaneously |     |

| 1      | Gain and offset are updated alternately    |     |

Table 29: Automatic compensation sequence control

Automatic compensation can be used in conjunction with temperature compensation. Automatic compensation will then remove any residual offset or gain mismatch not corrected by the temperature correction algorithm.

#### Limitation

The automatic compensation measures the amplitude and offset at the output of iC-TW3. In order to provide meaningful information the output signals must be of reasonable encoder quality at all times. They need to be 90° out of phase and most importantly the amplitude must be larger than 0.5 V peak-peak differential (larger than 0.25 V peak-peak single ended) whereas the offset must be less then +/- 0.25 V. In situations where the minimum amplitude is not guaranteed, e.g by removing the MR input sensor from the magnetic source, wrong offset and gain control correction data might be generated.

Rev B3, Page 20/26

#### **TEMPERATURE SENSING**

iC-TW3 contains an on-chip temperature sensor. Optionally, an external sensor can be used by setting bit *XCELSIUS* of register 0x02 to 1. An external temperature sensor is useful for remote temperature sensing or in situations where the internal sensor does not provide adequate accuracy. Also, device self-heating due to heavy output loads can have an impact on the internal sensor readings. Connect the external temperature sensor with its analog output to pin KELVIN.

| XCELSIUS | Addr. 0x02; bit 6                            | R/W |

|----------|----------------------------------------------|-----|

| Code     | Function                                     |     |

| 0        | Select internal temperature sensor (default) |     |

| 1        | Select external temperature sensor           |     |

Table 30: Temperature sensor select

An ADC converts the analog temperature signal into an 8-bit digital word. In case the on-chip sensor is used the 8-bit value spans a temperature range of -50 °C to 150 °C. It is recommended to calibrate the ADC using register 0x05 even when using an external temperature sensor.

#### Calibrating the temperature ADC

The raw ADC value can be accessed through register 0x40. A  $\pm 2$  increment hysteresis is applied to the ADC value to remove conversion noise and the offset register 0x05 is added. The final value is stored in register 0x12 and is used for temperature compensation.

To achieve best temperature accuracy it is required to calibrate the ADC by correctly programming register 0x05. At any known ambient temperature the register 0x05 is programmed such to read the expected ADC value. As an example, consider the product assembly floor with an ambient temperature of 20 °C. Due to device variation the ADC value read before calibration can be anything between 0 °C to 40 °C. Register 0x05 is now used to tune the ADC output value to the correct binary representation of 20 °C.

| CCELSIUS( | <b>3:0)</b> Addr. 0x05; bit 7:4 R/W                 | / |

|-----------|-----------------------------------------------------|---|

| Code      | Bit 3 is sign, bits 2:0 are magnitude of correction |   |

| 1111      | Most negative correction                            |   |

|           |                                                     |   |

| 1001      | Least negative correction                           |   |

| 1000      | No correction                                       |   |

| 0000      | No correction (default)                             |   |

| 0001      | Least positive correction                           |   |

|           |                                                     |   |

| 0111      | Most positive correction                            |   |

Table 31: Coarse offset correction

| FCELSIUS( | 3:0) Addr. 0x05; bit 3:0               | R/W       |

|-----------|----------------------------------------|-----------|

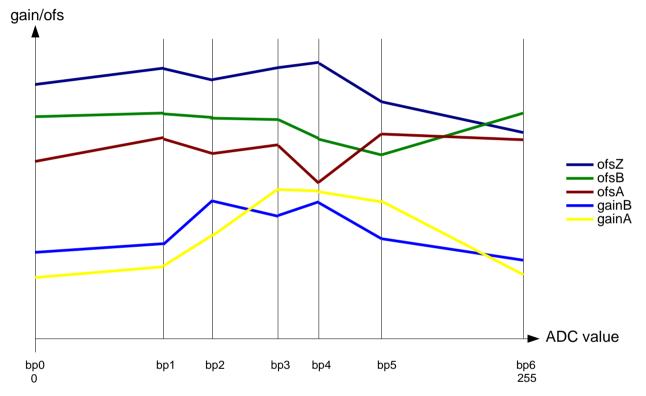

| Code      | Value added to ADC reading is FCELSIUS | (3:0) - 8 |